# Virtual memory (III): System Architecture and Design

Hung-Wei Tseng

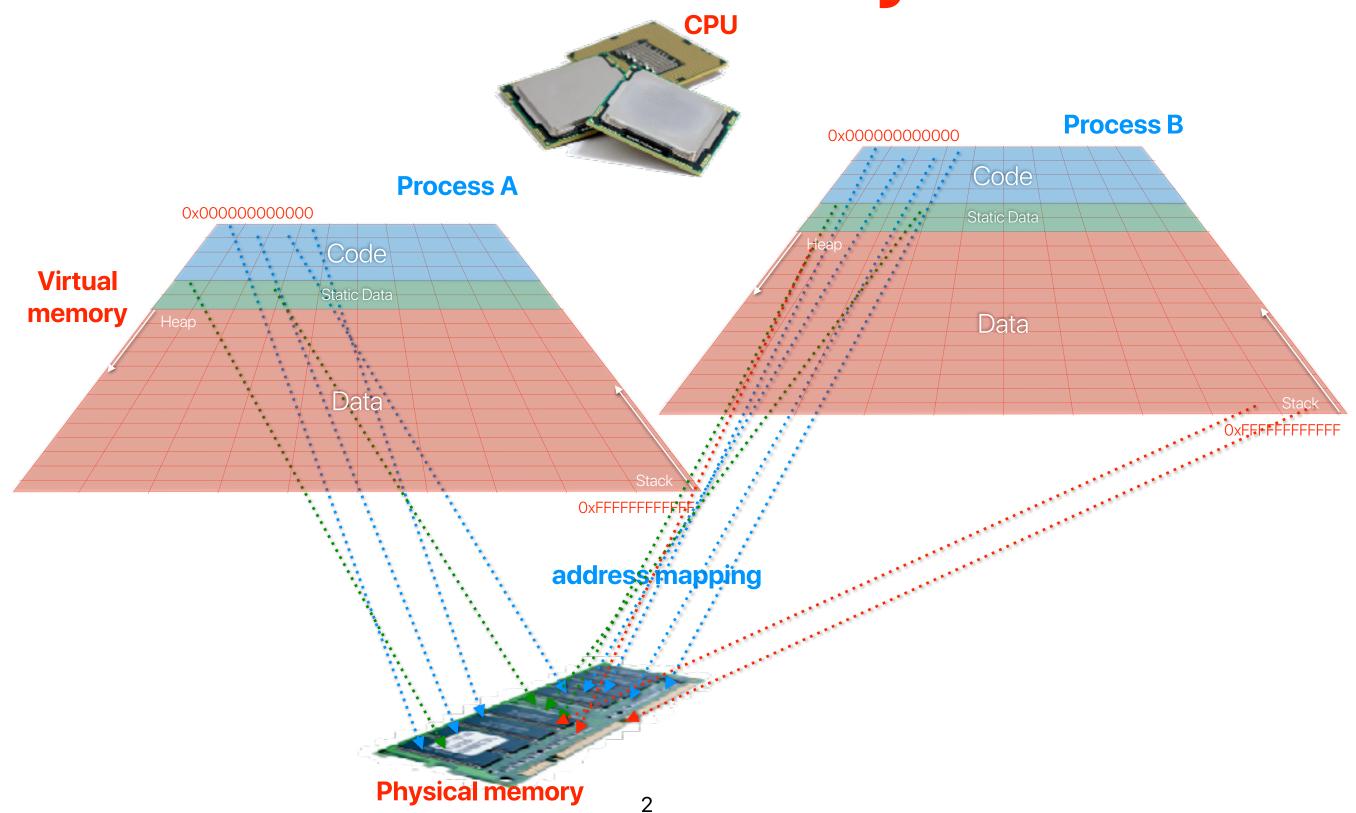

### Virtual Memory

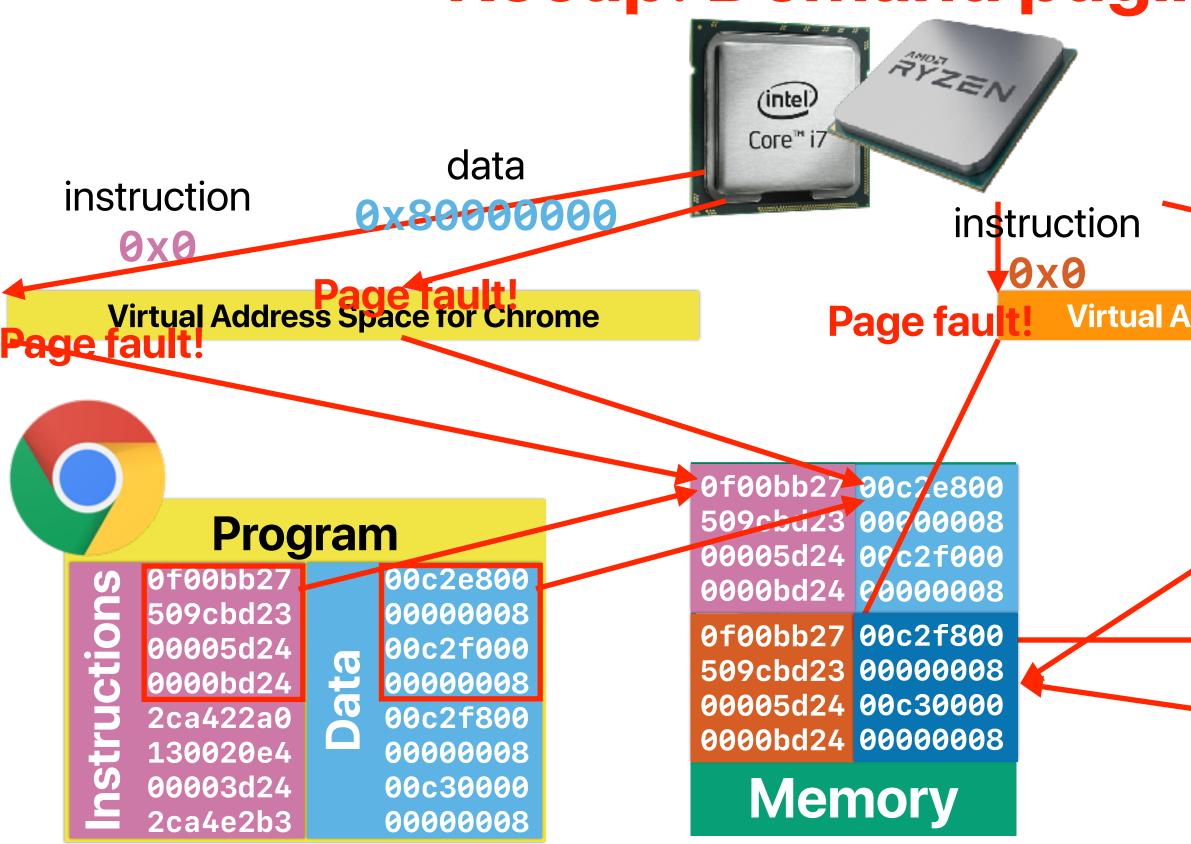

### **Recap: Demand paging**

#### data 0x80008000 **Virtual Address Space for Apple Music**

#### Program

Ծ

$\mathbf{G}$ **nstructi**

0f00bb27 509cbd23 00005d24 0000bd24 2ca422a0 130020e4 00003d24 2ca4e2b3

00c2e800 00000008 00c2f000 80000008 00c2f800 00000008 00c30000 00000008

### **Recap: Demand paging**

#### Application B

# Segmentation v.s. demand paging

- How many of the following statements is/are correct regarding segmentation and demand paging?

- Segments can cause more external fragmentations than demand paging — the main reason why we love paging!

Paging can still cause internal fragmentations— within a page

- The overhead of address translation in segmentation is higher you need to provide finer-grained mapping in paging you may need to handle page faults! Consecutive virtual memory address may not be consecutive in physical

- (4) address if we use demand paging

- A. 0

- B. 1

- C. 2

#### D. 3

E. 4

We haven't seen pure/true implementation of segmentations for a while, but we still use segmentation fault errors all the time!

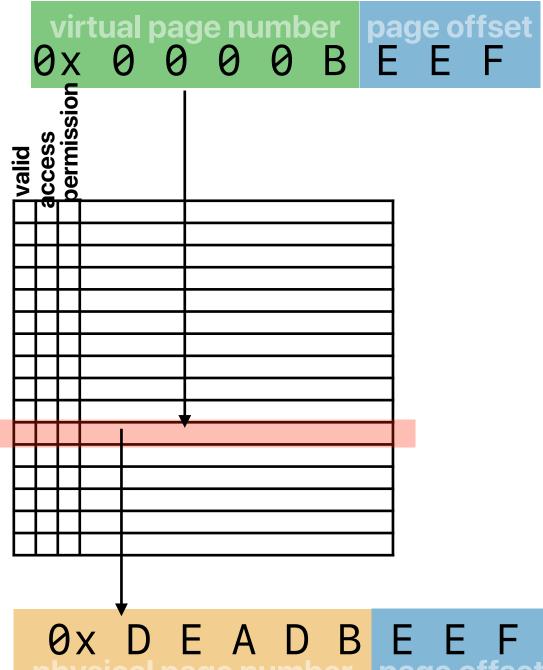

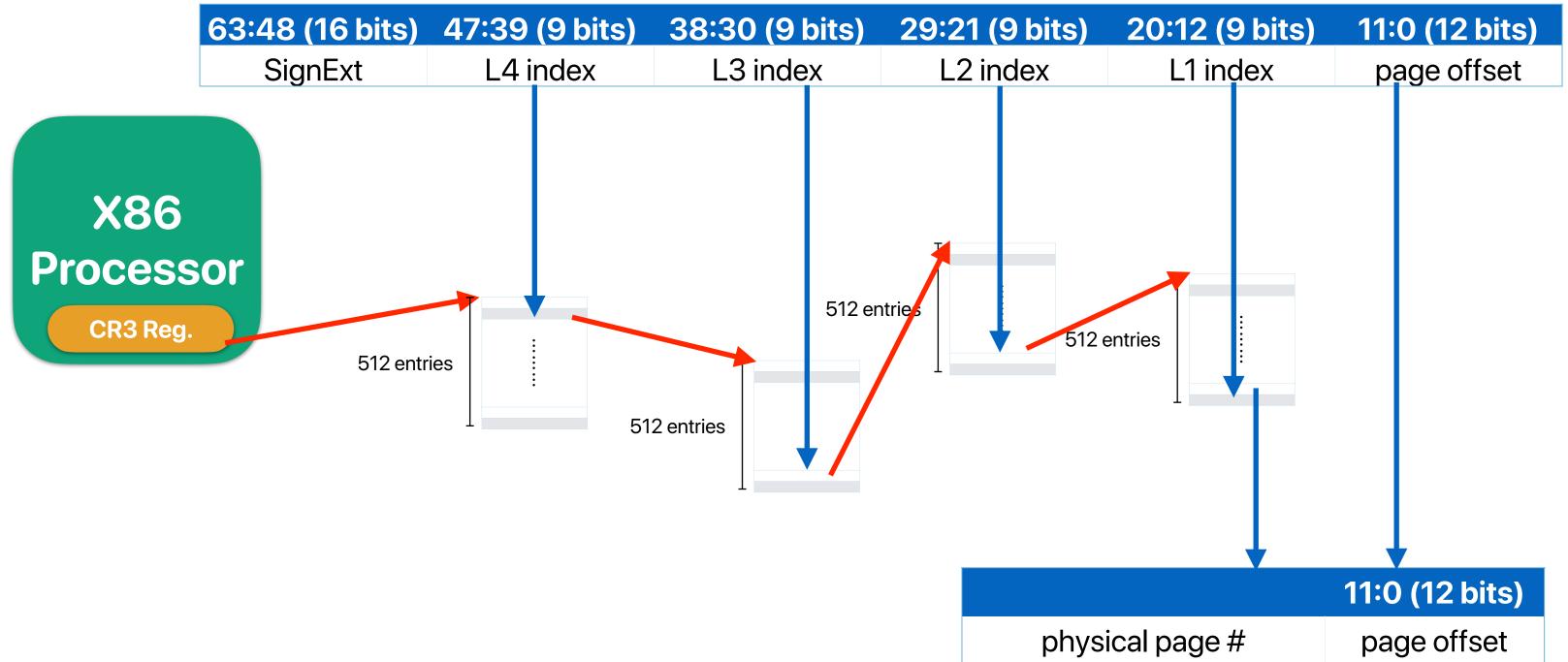

### **Recap: Address translation**

- Processor receives virtual addresses from the running code, main memory uses physical memory addresses

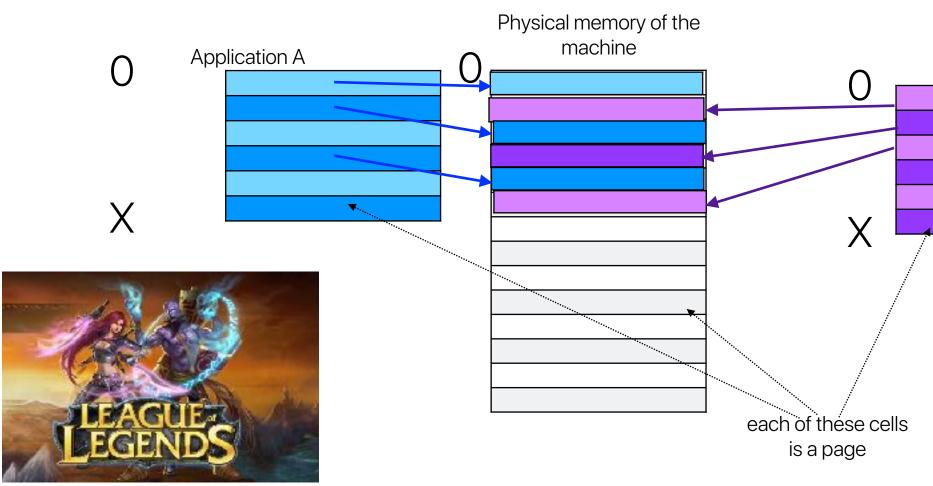

- Virtual address space is organized into "pages"

- The system references the **page table** to translate addresses

- Each process has its own page table

- The page table content is maintained by OS

- In addition to valid bit and physical page #, the page table may also store

- Reference bit

- Modified bit

- Permissions

Virtual address

Page

table

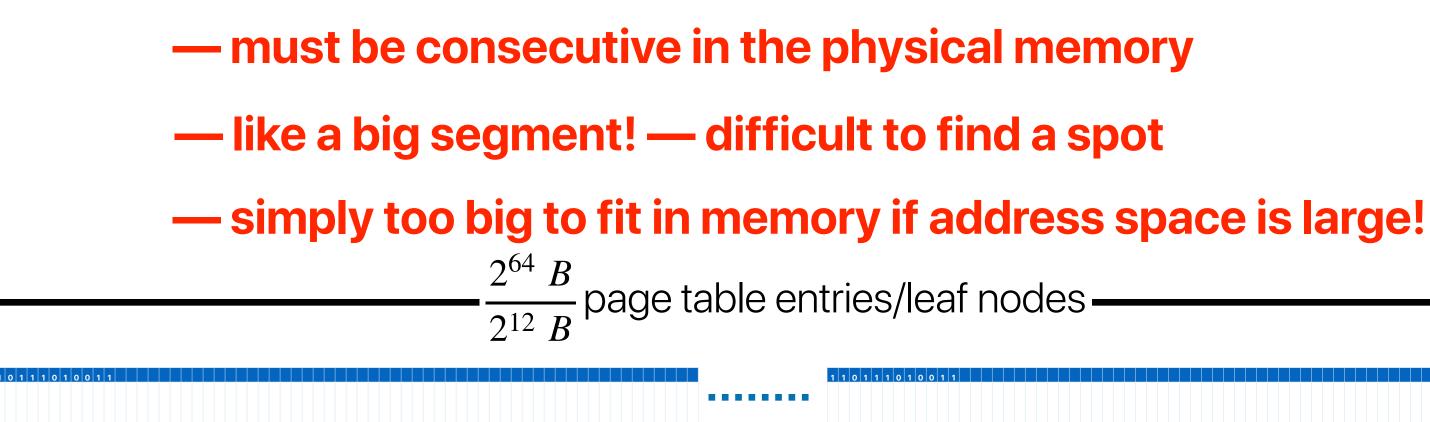

# **Recap: Size of page table**

- Assume that we have 64-bit virtual address space, each page is 4KB, each page table entry is 8 bytes (64-bit addresses), what magnitude in size is the page table for 32 processes?

- A. MB  $2^{20}$  Bytes

- B.  $GB 2^{30}$  Bytes

- D.  $PB 2^{50}$  Bytes

E.  $EB - 2^{60}$  Bytes

C. TB – 2<sup>40</sup> Bytes 8 bytes  $\frac{2^{64} B}{4 KB} = 2^{3}B \times \frac{2^{64} B}{2^{12} R} = 2^{55} B = 32 PB$  $32 PB \times 32 = 2^{60}B = 1 EB$

### **Conventional page table**

**Virtual Address Space**

#### 0xFFFFFFFFFFFFFFFF

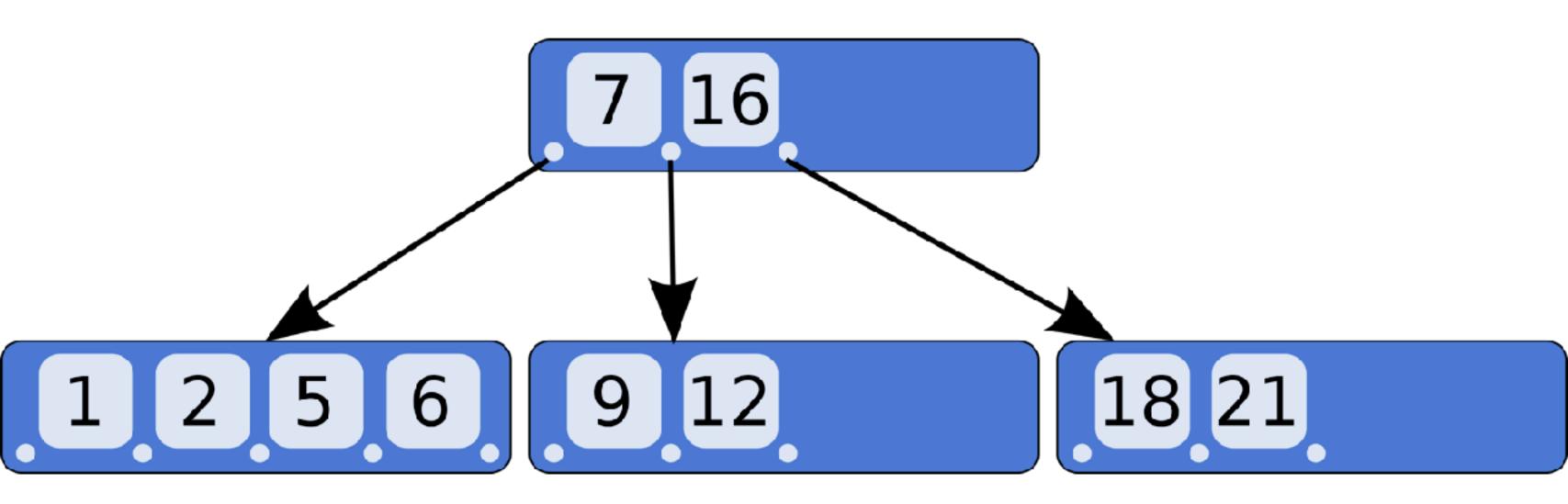

### "Paged" page table

#### **0**×FFFFFFFFFFFFFFF

# These nodes are spread out, how to locate them in the memory? 1 1 0 1 1 1 0 1 0 0 . 1

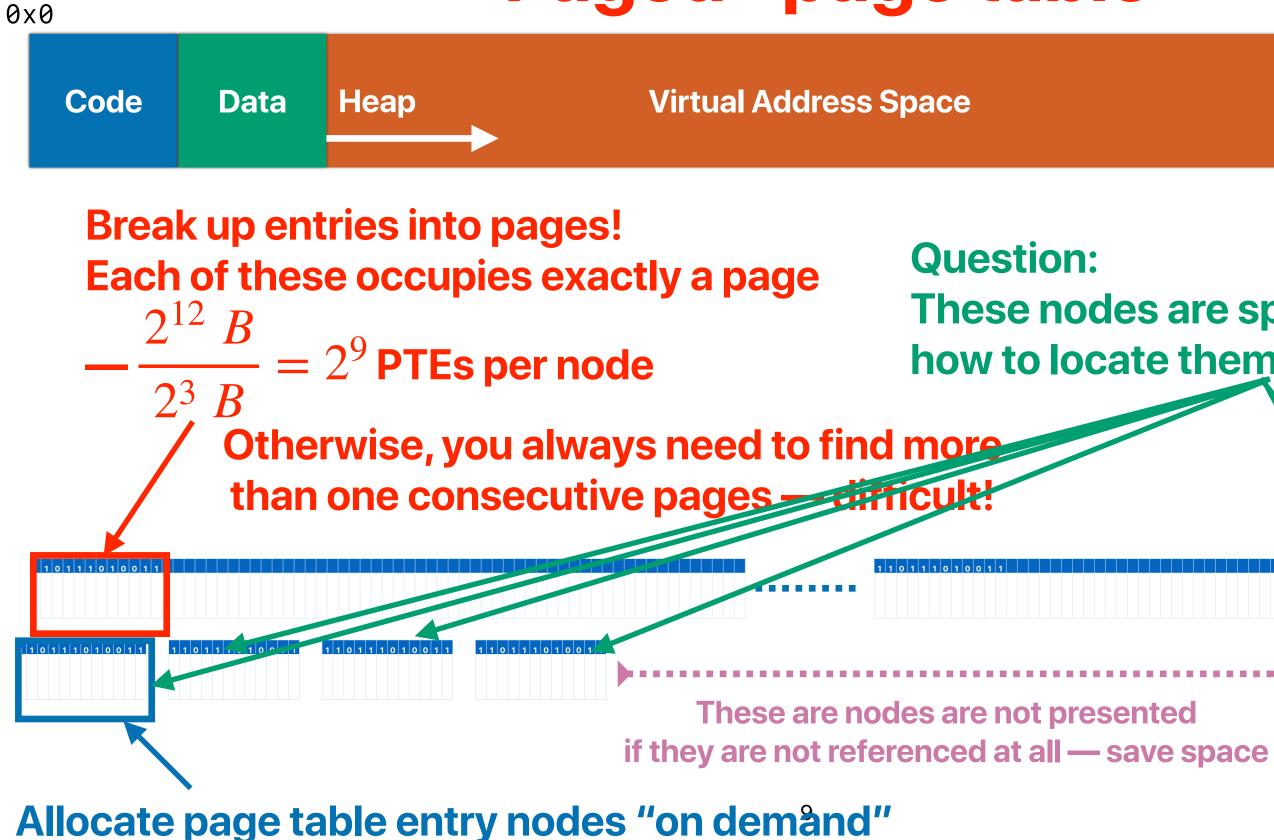

#### **B-tree**

https://en.wikipedia.org/wiki/B-tree#/media/File:B-tree.svg

### **Hierarchical Page Table**

#### **0**×FFFFFFFFFFFFFFF

### **Case study: Address translation in x86-64**

#### Recap: If we expose memory directly to the processor

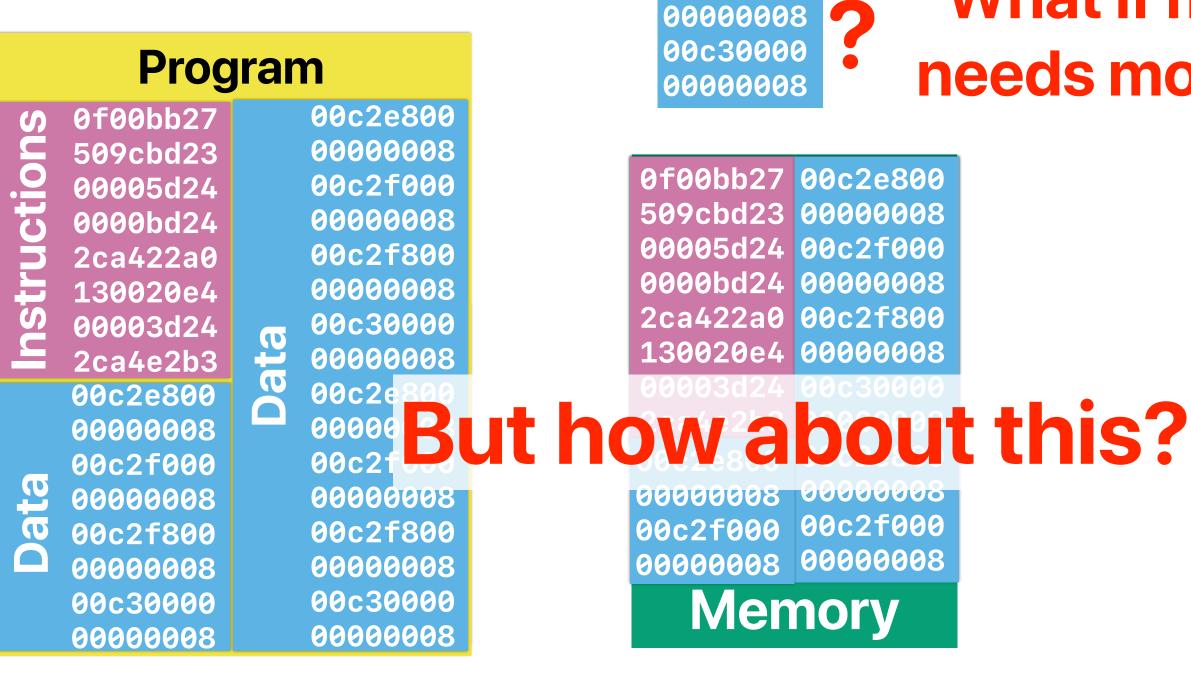

# What if both programs need to use memory?

0f00bb2700c2e800509cbd23000000800005d2400c2f0000000bd2400000082ca422a000c2f800

# Simply segmentation or paging helps on

**bbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbc**2**tbbcbc**2**tbbcbc**2**tbbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcbcb**

130020e4

00003d24

2ca4e2b3

Memory

this

# Property Diagonal Diagonal

#### Recap: If we expose memory directly to the processor (I)

00c2f800

# What if my program needs more memory?

#### **Recap:** If we expose memory directly to the processor (II)

What if my program runs on a machine with a different memory size?

### Program

| 5 | 0f00bb27 |     | 00c2e800 |

|---|----------|-----|----------|

|   | 509cbd23 |     | 00000008 |

|   | 00005d24 | σ   | 00c2f000 |

| 5 | 0000bd24 | Ita | 0000000  |

|   | 2ca422a0 | a   | 00c2f800 |

|   | 130020e4 |     | 00000008 |

| 5 | 00003d24 |     | 00c3000  |

|   | 2ca4e2b3 |     | 0000000  |

0f00bb27 00c2e800 509cbd23 0000008 00005d24 00c2f000 0000bd240000008 2ca422a0 00c2f800 130020e4 0000008

### **Current scoreboard**

- Swapping

- VAX/VMS Design

- Mach VM

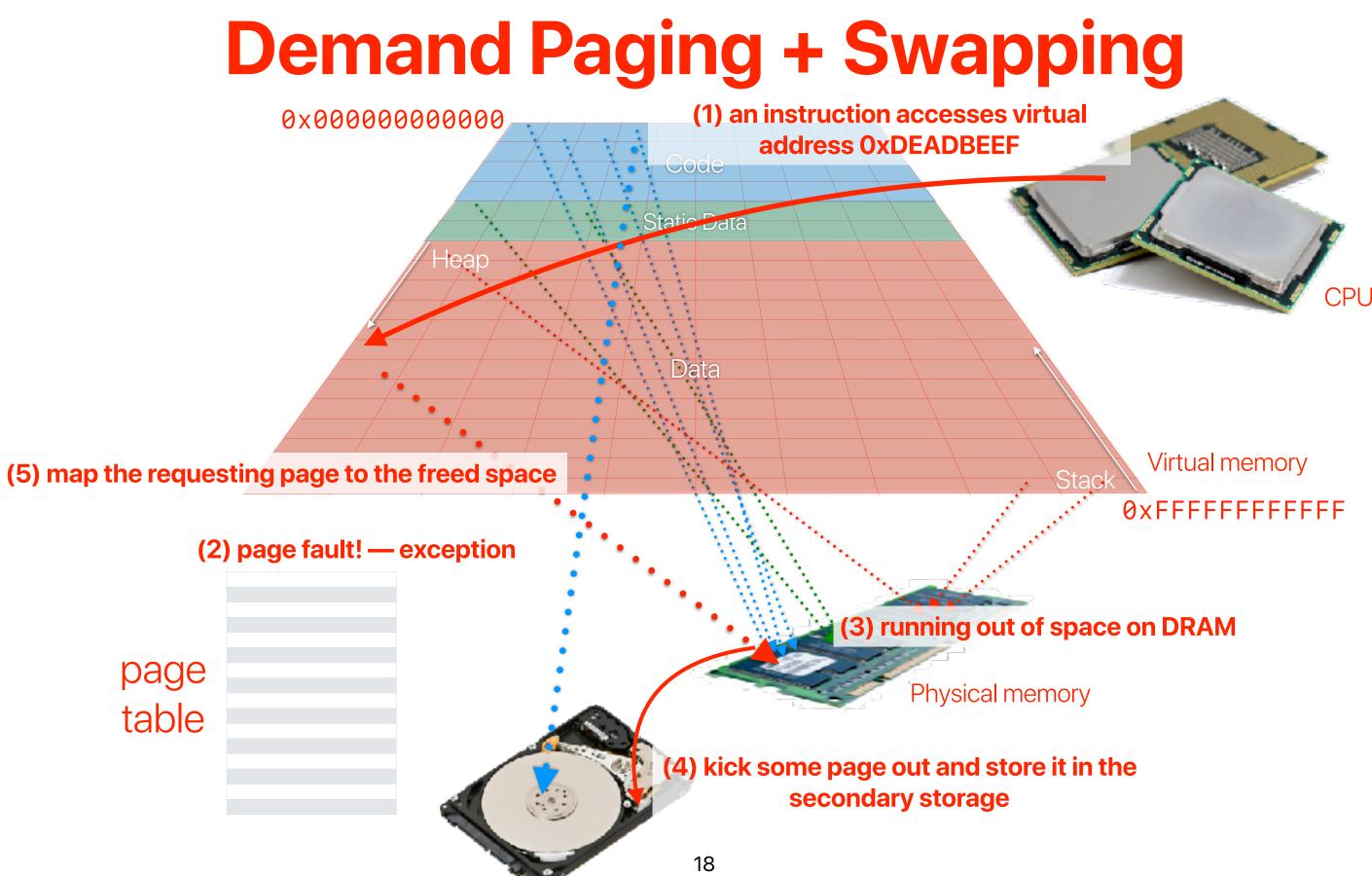

### The mechanism: demand paging + swapping

- Divide physical & virtual memory spaces into fix-sized units pages

- Allocate a physical memory page whenever the virtual memory page containing your data is absent

- In case if we are running out of physical memory

- Reserve space on disks

- Disks are slow: the access time for HDDs is around 10 ms, the access time for SSDs is around 30us - 1 ms

- Disks are orders of magnitude larger than main memory

- When you need to make rooms in the physical main memory, allocate a page in the swap space and put the content of the evicted page there

- When you need to reference a page in the swap space, make a room in the physical main memory and swap the disk space with the evicted page

### Latency Numbers Every Programmer Should Know (2020 Version)

| Operations                         | Latency (ns)   | Latency (us) | Latency (ms) |                             |

|------------------------------------|----------------|--------------|--------------|-----------------------------|

| L1 cache reference                 | 0.5 ns         |              |              | ~ 1 CPU cycle               |

| Branch mispredict                  | 3 ns           |              |              |                             |

| L2 cache reference                 | 4 ns           |              |              | 14x L1 cache                |

| Mutex lock/unlock                  | 17 ns          |              |              |                             |

| Send 2K bytes over network         | 44 ns          |              |              |                             |

| Main memory reference              | 100 ns         |              |              | 20x L2 cache, 200x L1 cache |

| Compress 1K bytes with Zippy       | 2,000 ns       | 2 us         |              |                             |

| Read 1 MB sequentially from memory | 3,000 ns       | 3 us         |              |                             |

| Read 4K randomly from SSD*         | 16,000 ns      | 16 us        |              |                             |

| Read 1 MB sequentially from SSD*   | 49,000 ns      | 49 us        |              |                             |

| Round trip within same datacenter  | 500,000 ns     | 500 us       |              |                             |

| Read 1 MB sequentially from disk   | 825,000 ns     | 825 us       |              |                             |

| Disk seek                          | 2,000,000 ns   | 2,000 us     | 2 ms         | 4x datacenter roundtrip     |

| Send packet CA-Netherlands-CA      | 150,000,000 ns | 150,000 us   | 150 ms       |                             |

https://colin-scott.github.io/personal\_website/research/interactive\_latency.html

21

- How much slower (approximately) is your average memory access time in a system when the probability of a page fault/ swapping is 0.1% comparing with the case when there is no page fault/swapping? (Assume you swap to a hard disk)

- A. 10x

- B. 100x

- C. 1000x

- D. 10000x

- E. 100000x

| Operations             |

|------------------------|

| L1 cache reference     |

| Branch mispredict      |

| L2 cache reference     |

| Mutex lock/unlock      |

| Main memory reference  |

| Compress 1K bytes wit  |

| Send 1K bytes over 1 G |

| Read 4K randomly from  |

| Read 1 MB sequentially |

| Round trip within same |

| Read 1 MB sequentially |

| Disk seek              |

| Read 1 MB sequentially |

|                        |

| Operations                         | Latency (ns)   |  |  |

|------------------------------------|----------------|--|--|

| L1 cache reference                 | 0.5 ns         |  |  |

| Branch mispredict                  | 5 ns           |  |  |

| L2 cache reference                 | 7 ns           |  |  |

| Mutex lock/unlock                  | 25 ns          |  |  |

| Main memory reference              | 100 ns         |  |  |

| Compress 1K bytes with Zippy       | 3,000 ns       |  |  |

| Send 1K bytes over 1 Gbps network  | 10,000 ns      |  |  |

| Read 4K randomly from SSD*         | 150,000 ns     |  |  |

| Read 1 MB sequentially from memory | 250,000 ns     |  |  |

| Round trip within same datacenter  | 500,000 ns     |  |  |

| Read 1 MB sequentially from SSD*   | 1,000,000 ns   |  |  |

| Disk seek                          | 10,000,000 ns  |  |  |

| Read 1 MB sequentially from disk   | 20,000,000 ns  |  |  |

| Send packet CA-Netherlands-CA      | 150,000,000 ns |  |  |

22

- How much slower (approximately) is your average memory access time in a system when the probability of a page fault/ swapping is 0.1% comparing with the case when there is no page fault/swapping? (Assume you swap to a hard disk)

- A. 10x

- B. 100x

- C. 1000x

- D. 10000x

- E. 100000x

| Operations             |

|------------------------|

| L1 cache reference     |

| Branch mispredict      |

| L2 cache reference     |

| Mutex lock/unlock      |

| Main memory reference  |

| Compress 1K bytes wit  |

| Send 1K bytes over 1 G |

| Read 4K randomly from  |

| Read 1 MB sequentially |

| Round trip within same |

| Read 1 MB sequentially |

| Disk seek              |

| Read 1 MB sequentially |

|                        |

| Operations                         | Latency (ns)   |  |  |

|------------------------------------|----------------|--|--|

| L1 cache reference                 | 0.5 ns         |  |  |

| Branch mispredict                  | 5 ns           |  |  |

| L2 cache reference                 | 7 ns           |  |  |

| Mutex lock/unlock                  | 25 ns          |  |  |

| Main memory reference              | 100 ns         |  |  |

| Compress 1K bytes with Zippy       | 3,000 ns       |  |  |

| Send 1K bytes over 1 Gbps network  | 10,000 ns      |  |  |

| Read 4K randomly from SSD*         | 150,000 ns     |  |  |

| Read 1 MB sequentially from memory | 250,000 ns     |  |  |

| Round trip within same datacenter  | 500,000 ns     |  |  |

| Read 1 MB sequentially from SSD*   | 1,000,000 ns   |  |  |

| Disk seek                          | 10,000,000 ns  |  |  |

| Read 1 MB sequentially from disk   | 20,000,000 ns  |  |  |

| Send packet CA-Netherlands-CA      | 150,000,000 ns |  |  |

- How much slower (approximately) is your average memory access time in a system when the probability of a page fault/swapping is 0.1% comparing with the case when there is no page fault/swapping? (Assume you swap to a hard disk)

- Memory (i.e. RAM) access time: 100ns •

- Disk access time: 10ms •

- P<sub>f</sub>: probability of a page fault

- Effective Access Time =  $100 \text{ ns} + P_f * 10^7 \text{ ns}$ •

- When  $P_f = 0.001$ : Effective Access Time = 10,100ns

- When  $P_f = 0.001$ , even with an SSD Effective Access Time =  $100 \text{ ns} + 10^{-3} * 10^{5}$ ns = 200 ns

- Takeaway: disk accesses are tolerable only • 23 when they are extremely rare

| Operations                         | Latency (ns)   |

|------------------------------------|----------------|

| L1 cache reference                 | 0.5 ns         |

| Branch mispredict                  | 5 ns           |

| L2 cache reference                 | 7 ns           |

| Mutex lock/unlock                  | 25 ns          |

| Main memory reference              | 100 ns         |

| Compress 1K bytes with Zippy       | 3,000 ns       |

| Send 1K bytes over 1 Gbps network  | 10,000 ns      |

| Read 4K randomly from SSD*         | 150,000 ns     |

| Read 1 MB sequentially from memory | 250,000 ns     |

| Round trip within same datacenter  | 500,000 ns     |

| Read 1 MB sequentially from SSD*   | 1,000,000 ns   |

| Disk seek                          | 10,000,000 ns  |

| Read 1 MB sequentially from disk   | 20,000,000 ns  |

| Send packet CA-Netherlands-CA      | 150,000,000 ns |

24

- How much slower (approximately) is your average memory access time in a system when the probability of a page fault/ swapping is 0.1% comparing with the case when there is no page fault/swapping? (Assume you swap to a hard disk)

- A. 10x

- B. 100x

- C. 1000x

- D. 10000x

- E. 100000x

| Operations                         | Latency (ns)   |  |  |  |  |

|------------------------------------|----------------|--|--|--|--|

| L1 cache reference                 | 0.5 ns         |  |  |  |  |

| Branch mispredict                  | 5 ns           |  |  |  |  |

| L2 cache reference                 | 7 ns           |  |  |  |  |

| Mutex lock/unlock                  | 25 ns          |  |  |  |  |

| Main memory reference              | 100 ns         |  |  |  |  |

| Compress 1K bytes with Zippy       | 3,000 ns       |  |  |  |  |

| Send 1K bytes over 1 Gbps network  | 10,000 ns      |  |  |  |  |

| Read 4K randomly from SSD*         | 150,000 ns     |  |  |  |  |

| Read 1 MB sequentially from memory | 250,000 ns     |  |  |  |  |

| Round trip within same datacenter  | 500,000 ns     |  |  |  |  |

| Read 1 MB sequentially from SSD*   | 1,000,000 ns   |  |  |  |  |

| Disk seek                          | 10,000,000 ns  |  |  |  |  |

| Read 1 MB sequentially from disk   | 20,000,000 ns  |  |  |  |  |

| Send packet CA-Netherlands-CA      | 150,000,000 ns |  |  |  |  |

# Page replacement policy

- Goal: Identify page to remove that will avoid future page faults (i.e. utilize) locality as much as possible)

- Implementation Goal: Minimize the amount of software and hardware overhead

- Example:

- Memory (i.e. RAM) access time: 100ns

- Disk access time: 10ms

- P<sub>f</sub>: probability of a page fault

- Effective Access Time =  $10^{-7} + P_f * 10^{-3}$

- When  $P_f = 0.001$ : Effective Access Time = 10,100ns

- Takeaway: Disk access tolerable only when it is extremely rare

### Virtual Memory Management in the VAX/ VMS Operating System H. M. Levy and P. H. Lipman Digital Equipment Corporation

# Why: The goals of VAX/VMS

- How many of the following statements is/are true regarding the optimization goals of VAX/VMS?

- ① Reducing the disk load of paging

- ② Reducing the startup cost of a program

- ③ Reducing the overhead of page tables

- ④ Reducing the interference from heavily paging processes

- A. 0

- B. 1

- C. 2

### D. 3

#### E. 4

# Why: The goals of VAX/VMS

- How many of the following statements is/are true regarding the optimization goals of VAX/VMS?

- ① Reducing the disk load of paging

- ② Reducing the startup cost of a program

- ③ Reducing the overhead of page tables

- ④ Reducing the interference from heavily paging processes

- A. 0

- B. 1

- C. 2

### D. 3

#### E. 4

# The "Why" behind VAX/VMS VM

- The system needs to execute various types of applications efficiently

Reducing the interference from heavily paging p

- The system runs on different types of hardware

Reducing the overhead of page tables

- As a result, the memory management system has to be capable of adjusting the changing demands characteristic of time sharing while allowing predictable performance required by real-time and batch processes

Reducing the startup cost of a program

Reducing the disk load of paging

time, timesnared (including program of perate on a family batch. In addition, VAX/VMS had to operate on a family of processors having different performance characterisof processors having different performance from 250K tics and physical memory capacities ranging from 250K

bytes to more than 8M bytes. To meet the requirement posed by these applications environments, the memor management system had to be capable of adjusting to the changing demands characteristic of timesharing while allowing the predictable performance required by real time and batch processes.

experience with a multitude of the provide a single entems, VAX/VMS was intended to provide a single environment for all VAX-based applications, whether realng processes including program development), or time, timeshases including program development), or batch. In addition, VAX/VMS had to operate on a family

# Why: The goals of VAX/VMS

- How many of the following statements is/are true regarding the optimization goals of VAX/VMS?

- ① Reducing the disk load of paging

- ② Reducing the startup cost of a program

- ③ Reducing the overhead of page tables

- ④ Reducing the interference from heavily paging processes

- A. 0

- **B**. 1

- C. 2

- D. 3

#### Poll close in 1:30

### What VAX/VMS proposed to achieve these goals?

Considering the optimization goals and the proposed VAX/ VMS mechanisms, which of the following combinations is incorrect?

|   | Goal                             |   | Opt             |

|---|----------------------------------|---|-----------------|

| Α | Process startup cost             | W | Demand-zero     |

| В | Process performance interference | Χ | Process-local i |

| С | Page table lookup overhead       | Y | Page clustering |

| D | Paging load on disks             | Ζ | Page caching    |

#### timization

- & copy-on-refernce

- replacement

- g

#### Poll close in 1:30

### What VAX/VMS proposed to achieve these goals?

Considering the optimization goals and the proposed VAX/ VMS mechanisms, which of the following combinations is incorrect?

|   | Goal                             |   | Opt             |

|---|----------------------------------|---|-----------------|

| Α | Process startup cost             | W | Demand-zero     |

| В | Process performance interference | Χ | Process-local i |

| С | Page table lookup overhead       | Y | Page clustering |

| D | Paging load on disks             | Ζ | Page caching    |

#### timization

- & copy-on-refernce

- replacement

- g

### What VAX/VMS proposed to achieve these goals?

Considering the optimization goals and the proposed VAX/ VMS mechanisms, which of the following combinations is incorrect?

| Goal |                                  |   | Opt             |

|------|----------------------------------|---|-----------------|

| Α    | Process startup cost             | W | Demand-zero     |

| В    | Process performance interference | Χ | Process-local   |

| С    | Page table lookup overhead       | Y | Page clustering |

| D    | Paging load on disks             | Ζ | Page caching    |

#### timization

- & copy-on-refernce

- replacement

- g

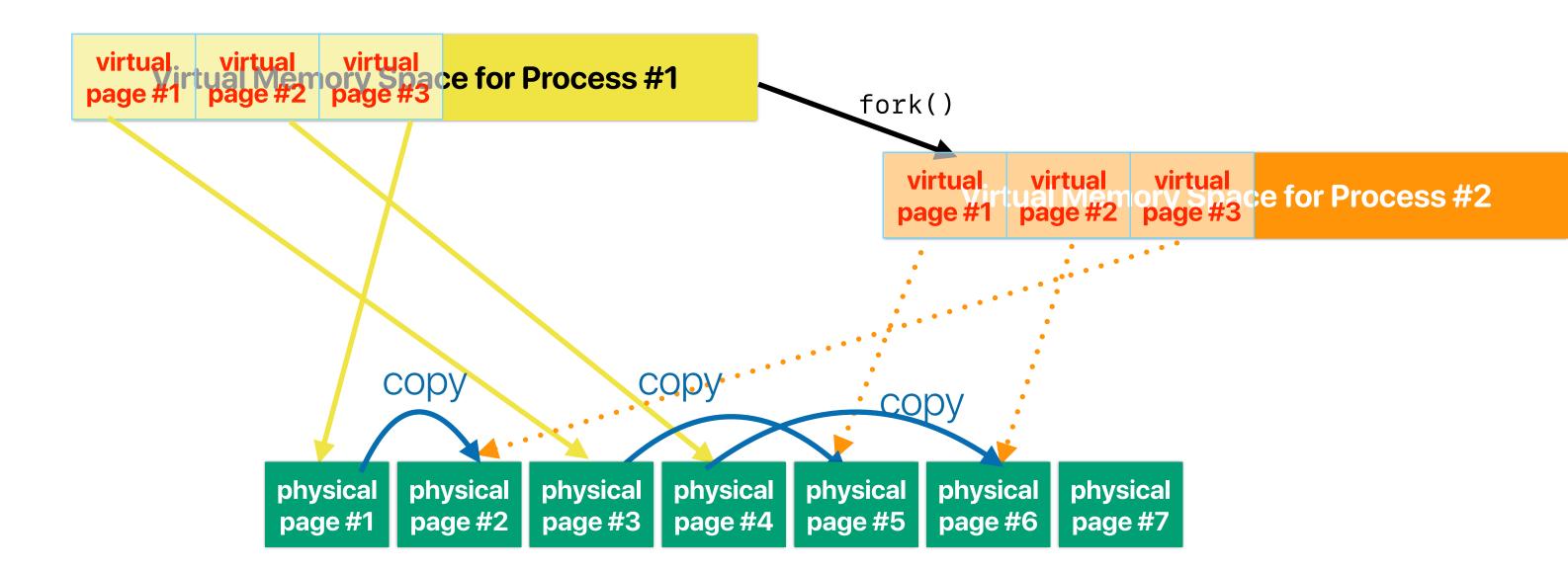

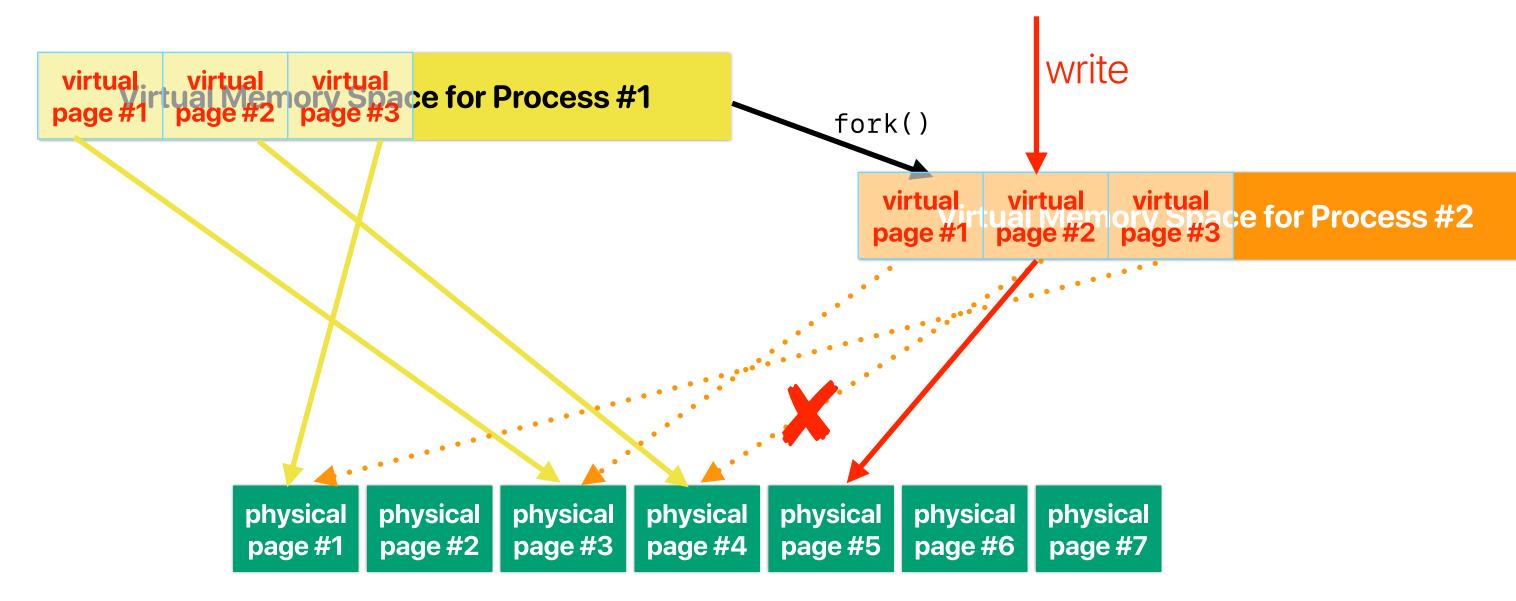

### What happens on a fork?

Copy the page content to different locations before the new process can start

### **Copy-on-write**

- The modified bit of a writable page will be set when it's loaded from the executable file

- The process eventually will have its own copy of that page

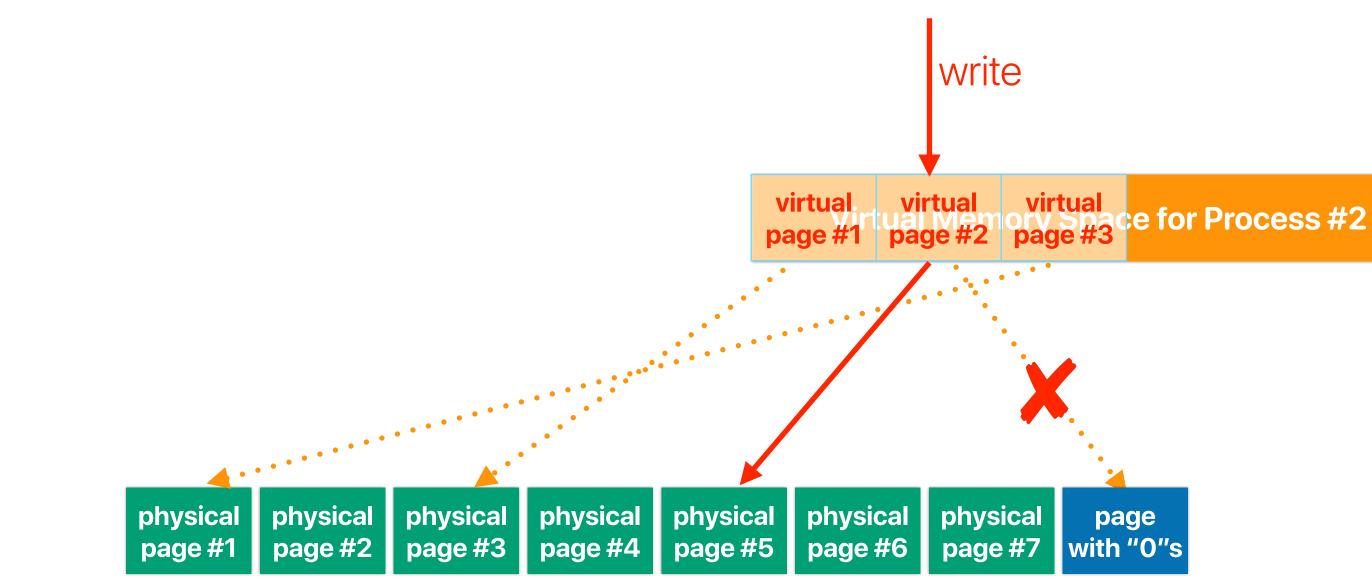

### **Demand zero**

- The linker does not embed the pages with all 0s in the compiled program

- When page fault occurs, allocate a physical page fills with zeros

- Set the modified bit so that the page can be written back

# d program

### What VAX/VMS proposed to achieve these goals?

Considering the optimization goals and the proposed VAX/ VMS mechanisms, which of the following combinations is incorrect?

|   | Goal                             |   | Opt             |

|---|----------------------------------|---|-----------------|

| 1 | Process startup cost             | W | Demand-zero     |

| В | Process performance interference | Χ | Process-local i |

| С | Page table lookup overhead       | Y | Page clustering |

| D | Paging load on disks             | Ζ | Page caching    |

### timization

- & copy-on-refernce

- replacement

- g

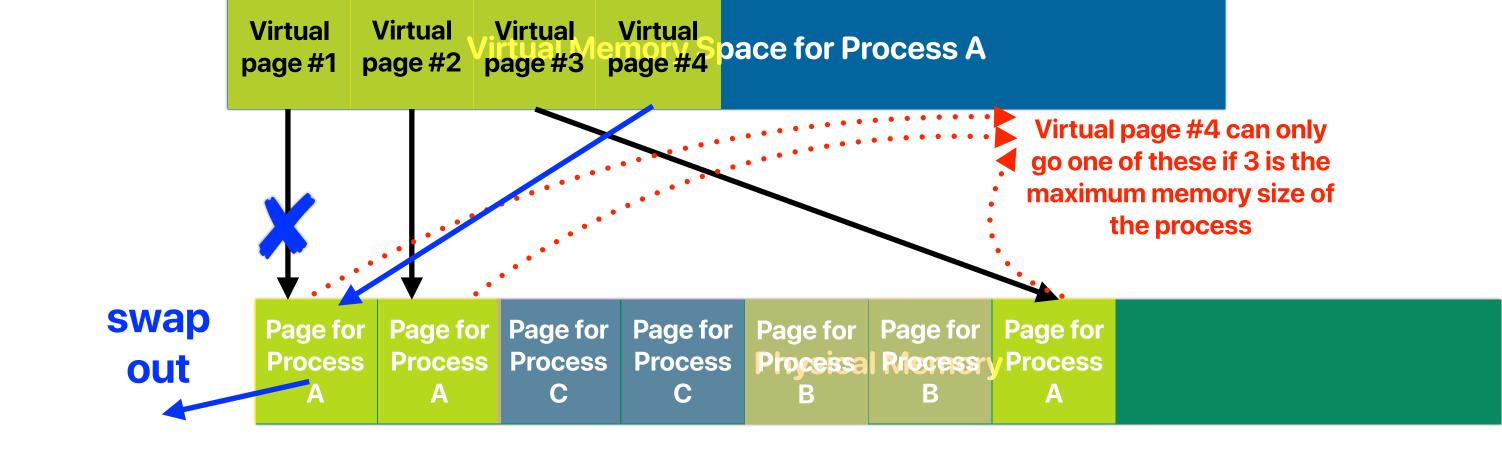

# Local page replacement policy

- Each process has a maximum size of memory

- When the process exceeds the maximum size, replaces from its own set of memory pages

- Control the paging behavior within each process

What's the policy? FIFO! Low overhead!

### What VAX/VMS proposed to achieve these goals?

Considering the optimization goals and the proposed VAX/ VMS mechanisms, which of the following combinations is incorrect?

|   | Goal                             |   | Opt             |

|---|----------------------------------|---|-----------------|

|   | Process startup cost             | W | Demand-zero     |

| P | Process performance interference | Χ | Process-local I |

| С | Page table lookup overhead       | Y | Page clustering |

| D | Paging load on disks             | Ζ | Page caching    |

### timization

- & copy-on-refernce

- replacement

- g

# Page clustering

- Read or write a cluster of pages that are both consecutive in virtual memory and the disk

- Combining consecutive writes into single writes

### Latency Numbers Every Programmer Should Know (2020 Version)

| Operations                                       | Latency (ns)   | Latency (us) | Latency (ms) |                             |  |

|--------------------------------------------------|----------------|--------------|--------------|-----------------------------|--|

| L1 cache reference                               | 0.5 ns         |              |              | ~ 1 CPU cycle               |  |

| Branch mispredict                                | 3 ns           |              |              |                             |  |

| L2 cache reference                               | 4 ns           |              |              | 14x L1 cache                |  |

| Mutex lock/unlock                                | 17 ns          |              |              |                             |  |

| Send 2K bytes over network                       | 44 ns          |              |              |                             |  |

| Main memory reference                            | 100 ns         |              |              | 20x L2 cache, 200x L1 cache |  |

| Compress 1K bytes with Zippy                     | 2,000 ns       | 2 us         |              |                             |  |

| Read 1 MB sequentially from memory               | 3,000 ns       | 3 us         |              |                             |  |

| Read 4K randomly from SSD*                       | 16,000 ns      | 16 us        |              |                             |  |

| Read 1 MB sequentially from SSD*a larger block i | sterns         | 49 us        |              |                             |  |

| Round trip within same datacenter                | 500,000 ns     | 500 us       |              |                             |  |

| Read 1 MB sequentially from disk                 | 825,000 ns (   | 825 us       |              |                             |  |

| Disk seek for a 512B sector                      | 2,000,000 ns   | 2,000 us     | 2 ms         | 4x datacenter roundtrip     |  |

| Send packet CA-Netherlands-CA                    | 150,000,000 ns | 150,000 us   | 150 ms       |                             |  |

https://colin-scott.github.io/personal\_website/research/interactive\_latency.html

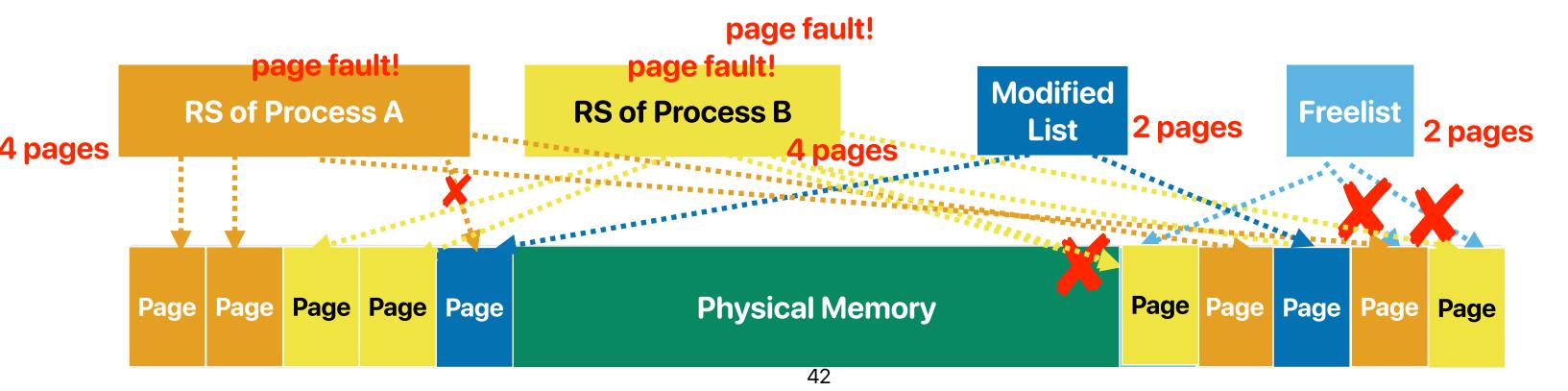

# Page caching to cover the performance loss

- Evicted pages will be put into one of the lists in DRAM

- Free list: clean pages

- Modified list: dirty pages needs to copy data to the disk

- Page fault to any of the page in the lists will bring the page back

- Reduces the demand of accessing disks

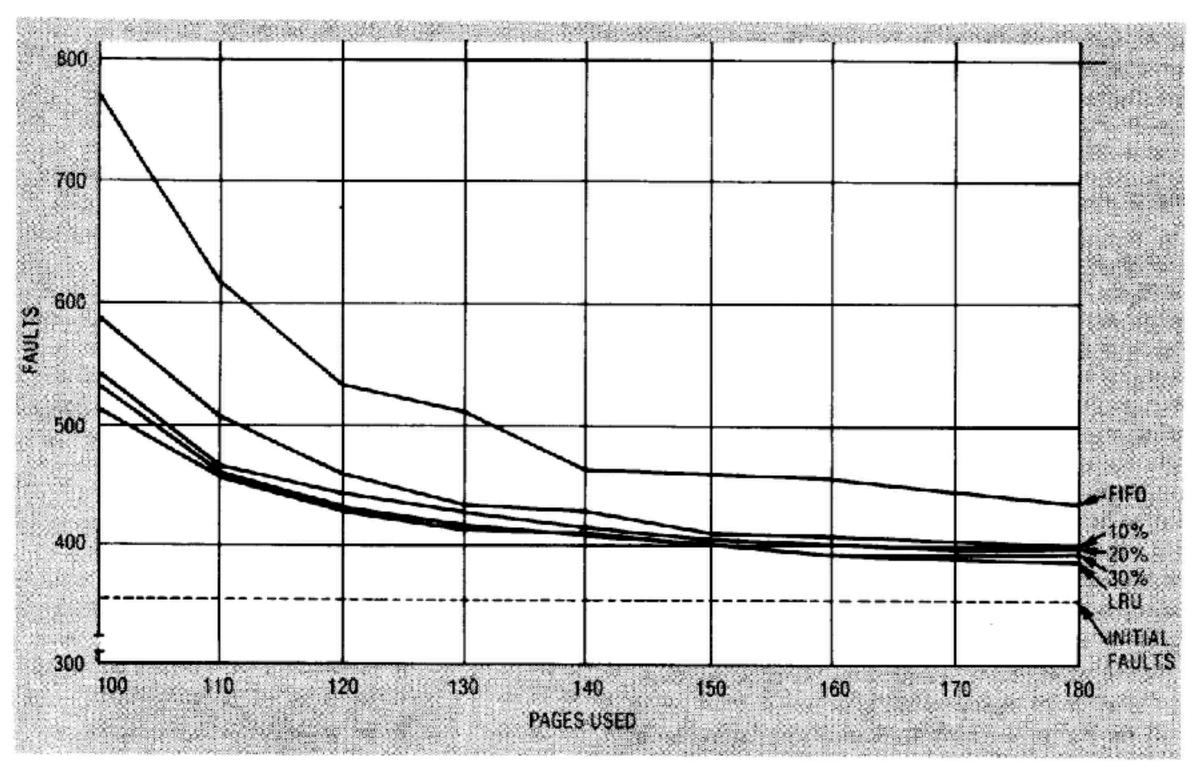

### Page caching

Figure 3. Faults vs. memory usage in Fortran compilation.

### What VAX/VMS proposed to achieve these goals?

Considering the optimization goals and the proposed VAX/ VMS mechanisms, which of the following combinations is incorrect?

| Goal                             |   | Opt             |

|----------------------------------|---|-----------------|

| Process startup cost             | W | Demand-zero     |

| Process performance interference | Χ | Process-local r |

| C Page table lookup overhead     | Y | Page clustering |

| Paging load on disks             | Ζ | Page caching    |

### timization

- & copy-on-refernce

- replacement

- also helps reduce disk loads

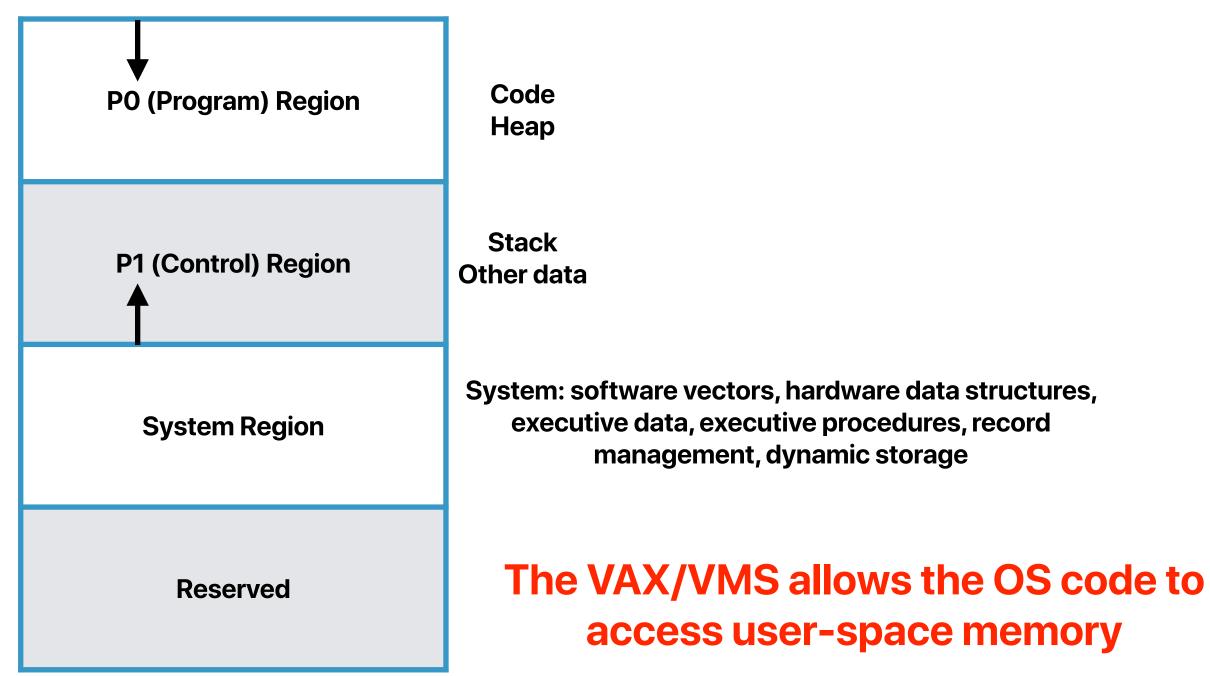

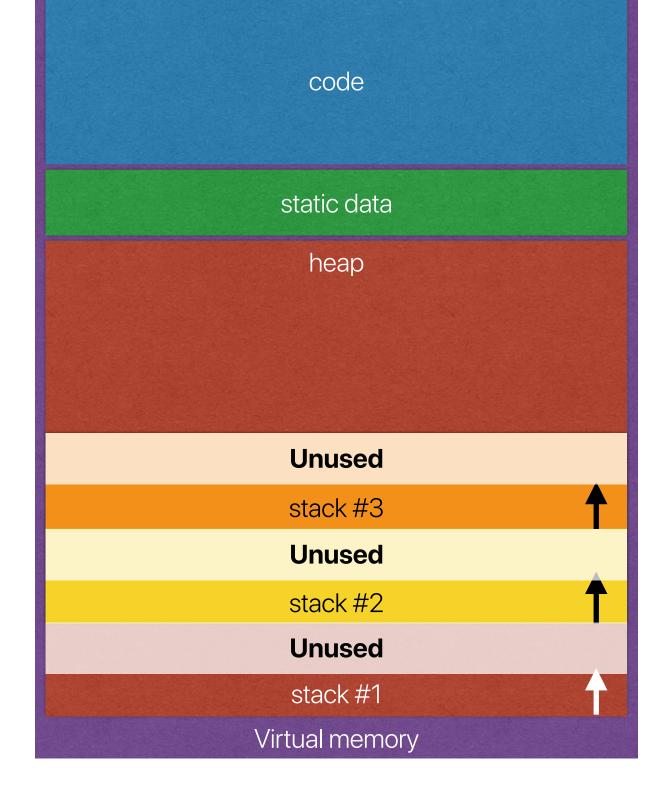

### **Process memory layout**

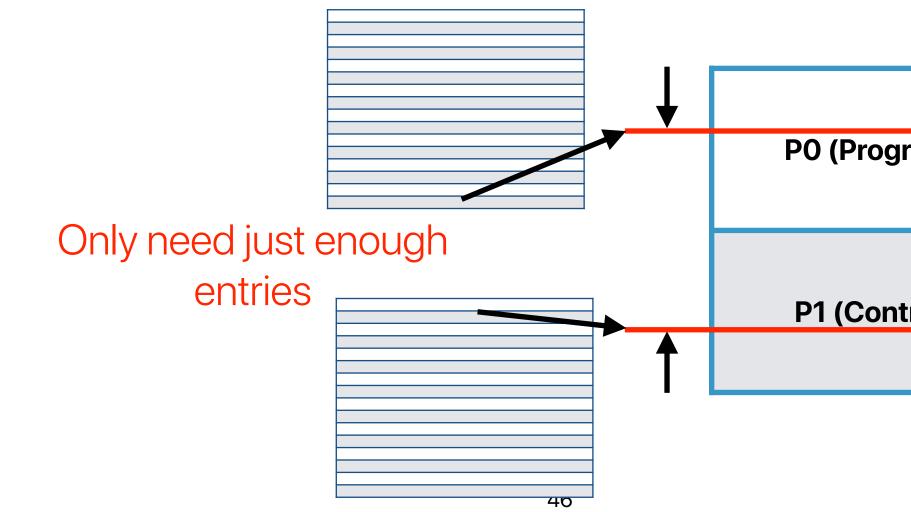

# Why segmented layout?

- Each segment has its own page table

- Entries between stack and heap boundaries do not need to be allocated — reduce the size of page table

**PO (Program) Region**

P1 (Control) Region

### What VAX/VMS proposed to achieve these goals?

Considering the optimization goals and the proposed VAX/ VMS mechanisms, which of the following combinations is incorrect?

| Goal                             |   | Opt             |

|----------------------------------|---|-----------------|

| Process startup cost             | W | Demand-zero     |

| Process performance interference | X | Process-local r |

| C Page table lookup overhead     | Υ | segmented n     |

| Paging load on disks             | Ζ | Page caching    |

### timization

- & copy-on-refernce

- replacement

- memory layout

# The impact of VAX/VMS

- VAX is popular in universities and UNIX is later ported to VAX — a popular OS research platform

- Affect the UNIX virtual memory design

- Affect the Windows virtual memory design

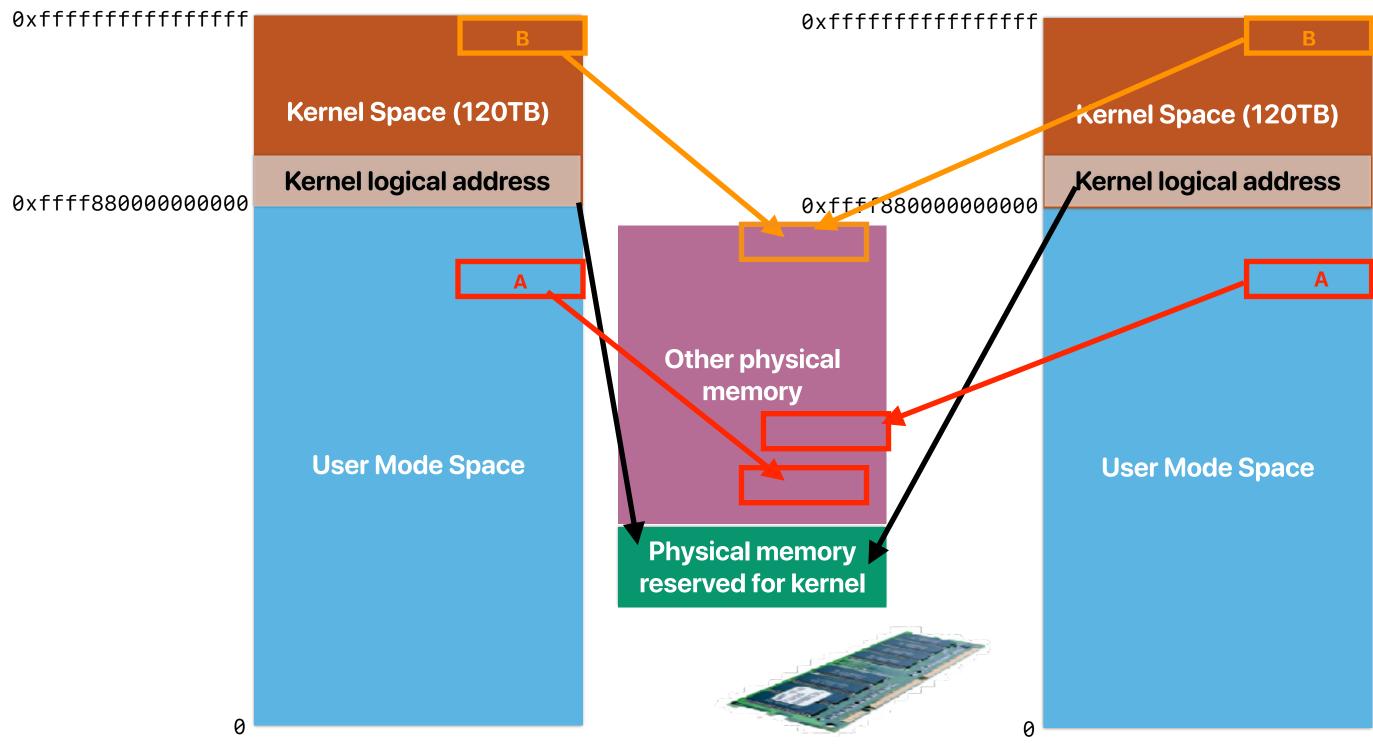

# 64-bit Linux process memory layout

### Machine-Independent Virtual Memory Management for Paged Uniprocessor and Multiprocessor Architectures Richard Rashid, Avadis Tevanian, Michael Young, David Golub, Robert Baron, David Black,

Richard Rashid, Avadis Tevanian, Michael Young, David Golub, Robert Bard William Bolosky, and Jonathan Chew Carnegie-Mellon University, NeXT, University of Rochester

# Mach abstractions

- Task: process in UNIX

- Thread: the basic scheduling identity

- Port: message queues protected by the kernel

- Message: data objects for inter-thread communication

- Memory object: data mapped into the address space of a task/ process

### We mentioned previously

### unication s space of a task/

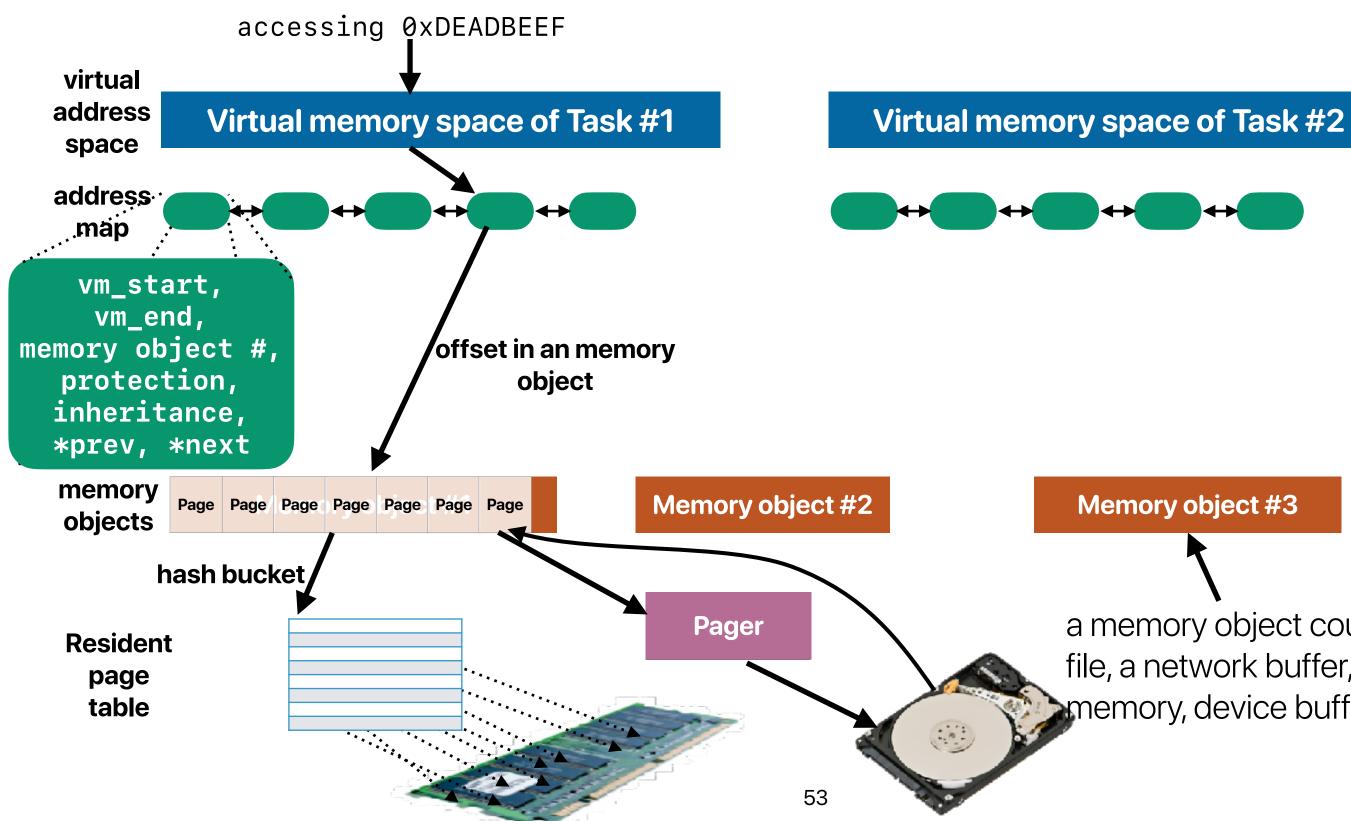

# What Mach VM proposed?

- Machine-independent virtual memory design by maintaining all VM state in a machine-independent module

- Treat hardware page tables/TLBs as caches of machineindependent information

### **Overview of Mach's VM**

a memory object could be anything — a file, a network buffer, remote network memory, device buffer, or physical DRAM

# Where is pmap?

- Pmap is just a cache of virtual to physical address mapping

- It accelerates address translation by caching the address mapping, but not required

- As a result, it can be a small as several KBs

### ress mapping he address

# The impact of Mach VM

- MacOS X uses a "hybrid" kernel BSD + Mach

- The kernel itself is BSD-based modular, not microkernelbased

- MacOS X's virtual memory resembles the Mach VM design

- Why?

- MacOS does not adopt the microkernel idea from Mach but takes Mach's VMS design instead of a VAX/UNIX style one. Why?

- ① Mach's VM would provide better average memory access latency

- ② Mach's VM would make the page table more efficient for sparse address allocations

- ③ Mach's VM would make the process creation more efficient

- ④ Mach's VM would be less dependent on hardware architecture

- A. 0

- B. 1

- C. 2

- D. 3

### E. 4

- MacOS does not adopt the microkernel idea from Mach but takes Mach's VMS design instead of a VAX/UNIX style one. Why?

- ① Mach's VM would provide better average memory access latency

- ② Mach's VM would make the page table more efficient for sparse address allocations

- ③ Mach's VM would make the process creation more efficient

- ④ Mach's VM would be less dependent on hardware architecture

- A. 0

- B. 1

- C. 2

- D. 3

### E. 4

- MacOS does not adopt the microkernel idea from Mach but takes Mach's VMS design instead of a VAX/UNIX style one. Why?

- Mach's VM would provide better average memory access latency — both of them uses FIFO by default + Mach has more context switches

Mach's VM would make the page table more efficient for sparse address — think about it's linked-list nature allocations

- ③ Mach's VM would make the process creation more efficient

- ④ Mach's VM would be less dependent on hardware architecture

- A. 0

- B. 1

- C. 2

### D. 3

### E. 4

### Address allocation is sparse in multithreading model!

- MacOS does not adopt the microkernel idea from Mach but takes Mach's VMS design instead of a VAX/UNIX style one. Why?

- Mach's VM would provide better average memory access latency — both of them uses FIFO by default + Mach has more context switches

Mach's VM would make the page table more efficient for sparse address — think about it's linked-list nature

- allocations - what's the benefit? - multithreading!

- Mach's VM would make the process creation more efficient

Mach's VM would be less dependent on hardware architecture

- A. 0

— what's the title of the paper?

- **B**. 1

- D. 3

## Announcement

- Reading quizzes due next Tuesday

- New office hour

- M 3p-4p and Th 9a-10a

- Use the office hour Zoom link, not the lecture one

- Project released

- Groups in 2

- Pull the latest version had some changes for later kernel versions https://github.com/hungweitseng/CS202-ResourceContainer

- Install an Ubuntu Linux 16.04.07 VM as soon as you can!

- Please do not use a real machine you may not be able to reboot again

- Midterm

- Will release on 2/10/2021 0:00am and due on 2/15/2021 11:59:00pm

- You will have to find a consecutive, non-stop 80-minute slot with this period

- One time, cannot reinitiate please make sure you have a stable system and network

- No late submission is allowed

Computer Science & Engineering