# Speculative Execution & Multithreaded Processor Architectures

Hung-Wei Tseng

#### Recap: addressing hazards

- Structural hazards

- Stall

- Modify hardware design

- Control hazards

- Stall

- Static prediction

- Dynamic prediction

- Data hazards

- Stall

- Data forwarding

- Dynamic Scheduling

#### What do you need to execution an instruction?

- Whenever the instruction is decoded put decoded instruction somewhere

- Whenever the inputs are ready all data dependencies are resolved

- Whenever the target functional unit is available

- This instruction has completed its own work in the current stage

- No other instruction is occupying the next stage

- The next stage has all its inputs ready

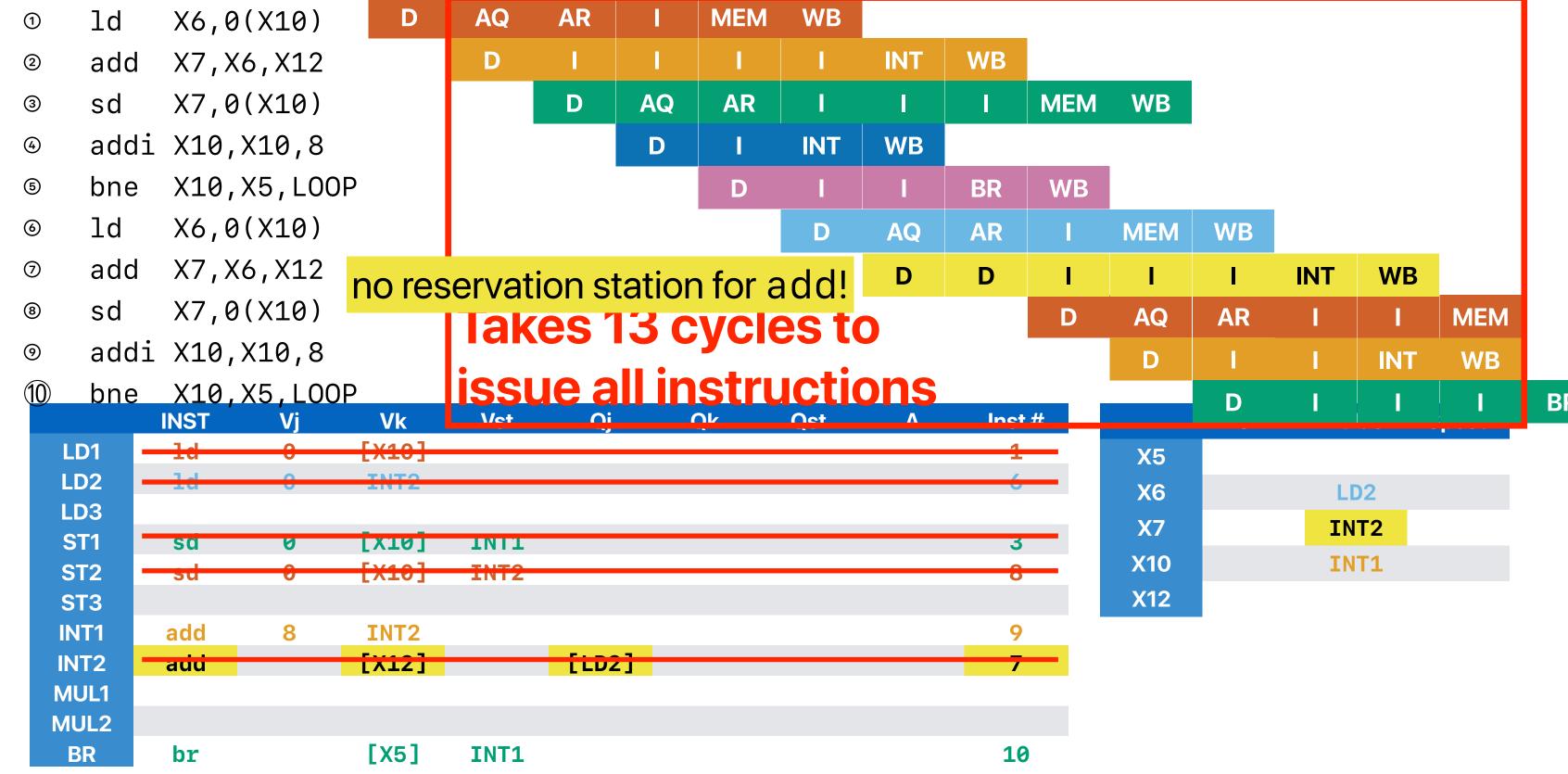

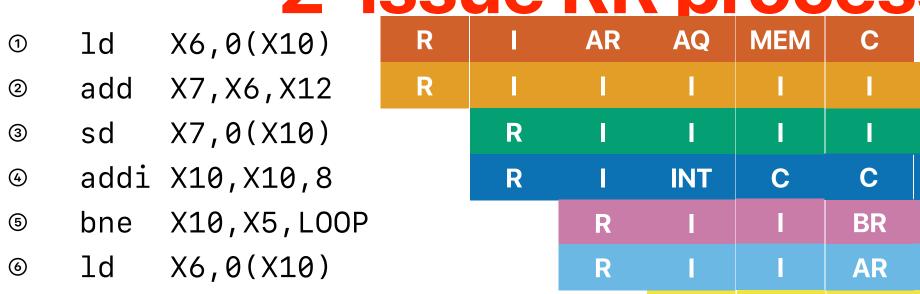

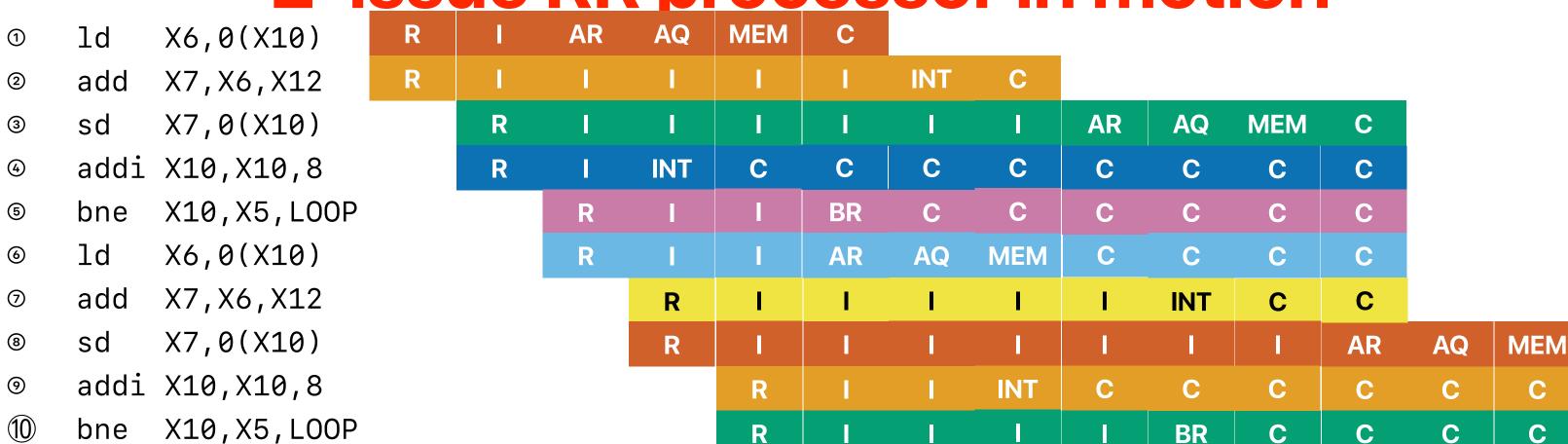

Tomasulo in motion

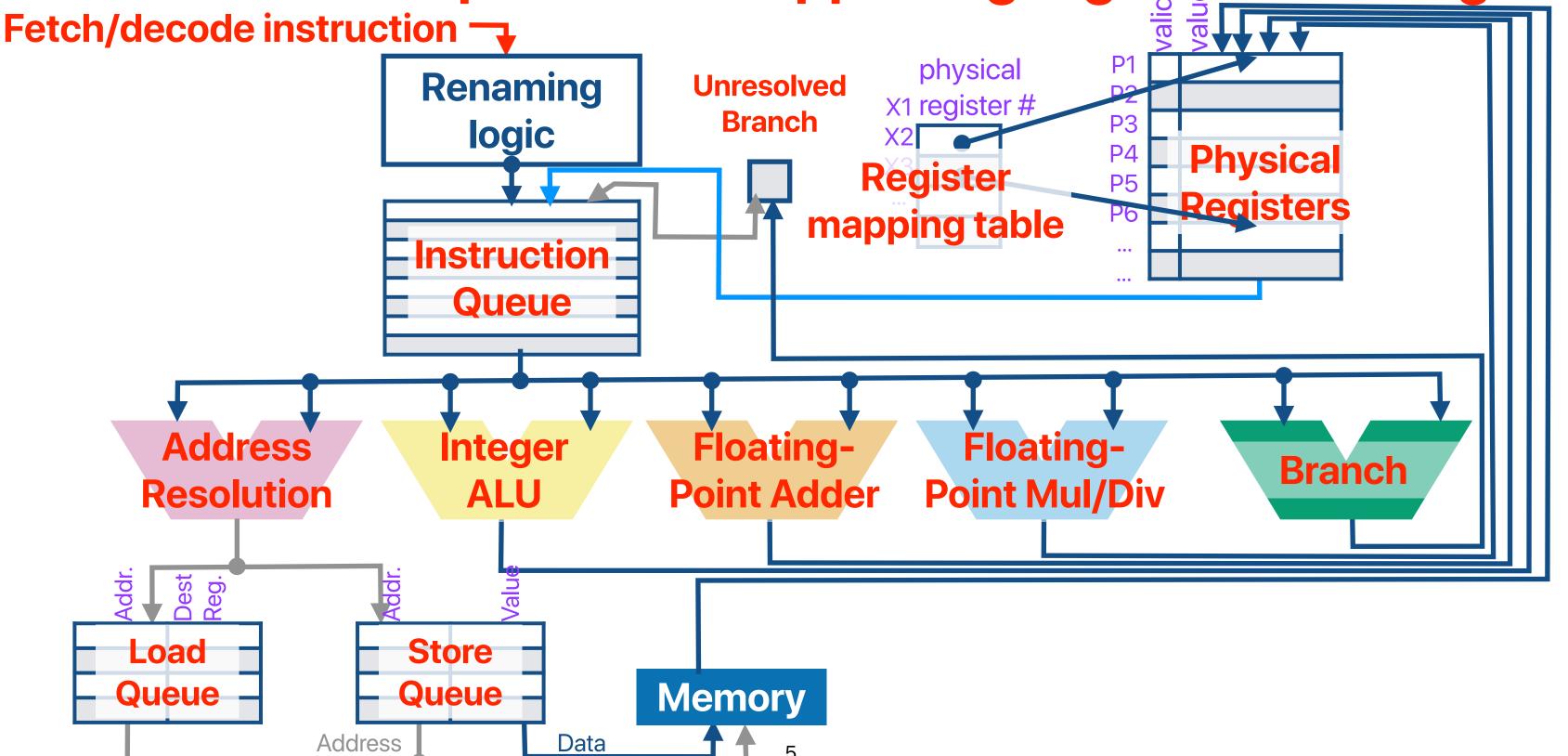

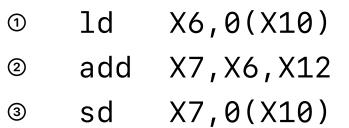

Overview of a processor supporting register renaming

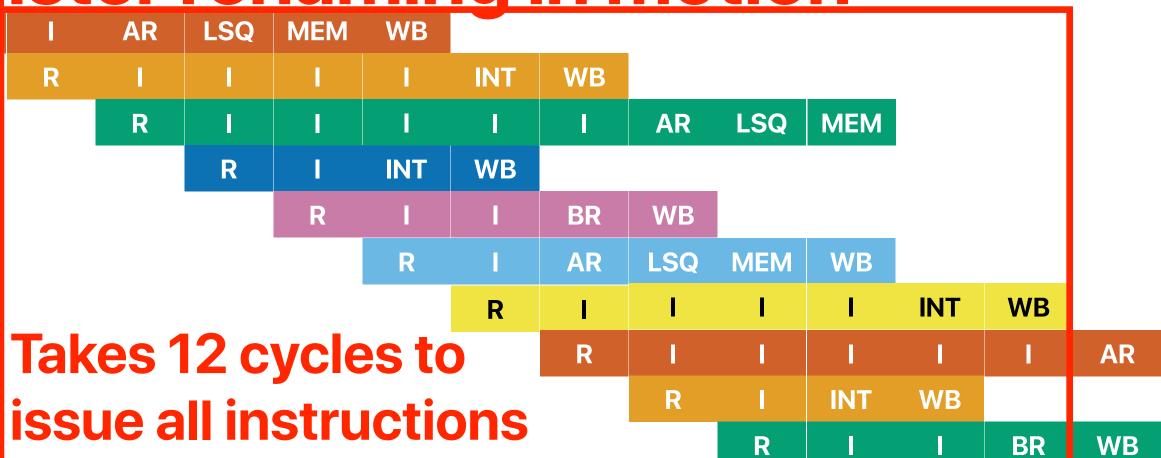

Register renaming in motion

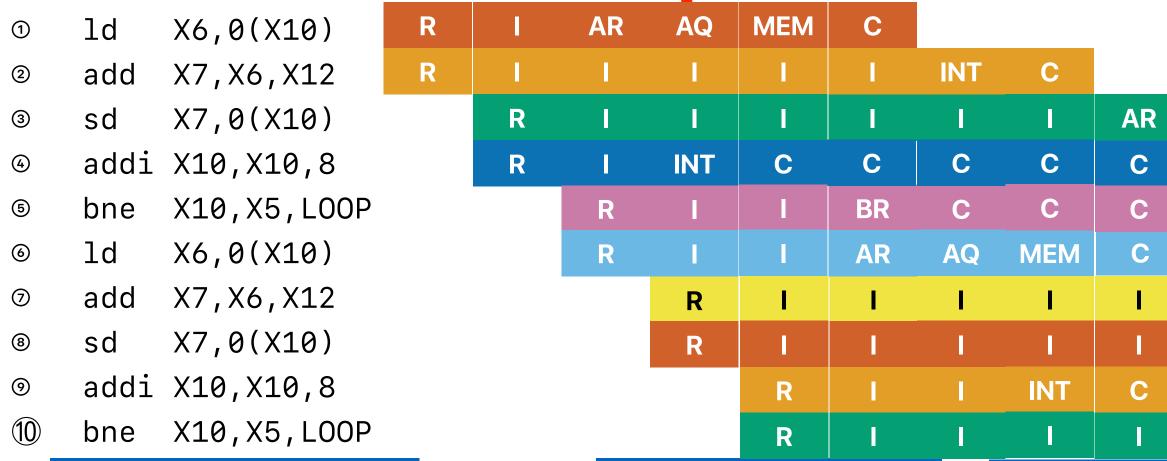

| 1 | ld  | X6,0(X10) |

|---|-----|-----------|

| 2 | add | X7,X6,X12 |

- 3 sd X7,0(X10)

- @ addi X10,X10,8

- ⑤ bne X10,X5,L00P

- © ld X6,0(X10)

- ② add X7,X6,X12

- sd X7,0(X10)

- addi X10,X10,8

- 10 bne X10, X5, LOOP

|     | Renamed instruction |              |  |  |  |  |  |  |  |

|-----|---------------------|--------------|--|--|--|--|--|--|--|

| 1 - | <del>ld</del>       | P1, 0(X10)   |  |  |  |  |  |  |  |

| 2 - | add                 | P2, P1, X12  |  |  |  |  |  |  |  |

| 3 - | <del>3d</del>       | P2, 0(X10)   |  |  |  |  |  |  |  |

| 4 - | addi                | P3, X10, 8   |  |  |  |  |  |  |  |

| 5 - | bne                 | P3, X5, L00P |  |  |  |  |  |  |  |

| 6 - | 14                  | P4, 0(P3)    |  |  |  |  |  |  |  |

| 7 - | add                 | P5, P1, X12  |  |  |  |  |  |  |  |

| 8   | sd                  | P5, 0(P3)    |  |  |  |  |  |  |  |

| 9 - | addi                | P6, P3, 8    |  |  |  |  |  |  |  |

| 10- | hne                 | P6, 0(X10)   |  |  |  |  |  |  |  |

| Physical Register |    |  |  |  |  |  |

|-------------------|----|--|--|--|--|--|

| <b>X5</b>         |    |  |  |  |  |  |

| X6                | P1 |  |  |  |  |  |

| <b>X7</b>         | P5 |  |  |  |  |  |

| X10               | Р3 |  |  |  |  |  |

| X12               |    |  |  |  |  |  |

|    | Valid | Value | In use |           | Valid | Value | In use |

|----|-------|-------|--------|-----------|-------|-------|--------|

| P1 | 1     |       | 1      | P6        | 1     |       | 1      |

| P2 | 1     |       | 1      | <b>P7</b> |       |       |        |

| Р3 | 1     |       | 1      | P8        |       |       |        |

| P4 | 1     |       | 1      | <b>P9</b> |       |       |        |

| P5 | 1     |       | 1      | P10       |       |       |        |

LS

Overview of a processor supporting register renaming Fetch/decode instruction physical Renaming **Unresolved** X1 register # What if we widen the **Branch** logic **Physical** pipeline to fetch/issue Register Registers two instructions at the mapping table nstruction same time? Queue Floating-Floating-Address Integer **Branch Point Mul/Div Point Adder** Resolution **ALU Store** Load Memory Queue Queue Data Address

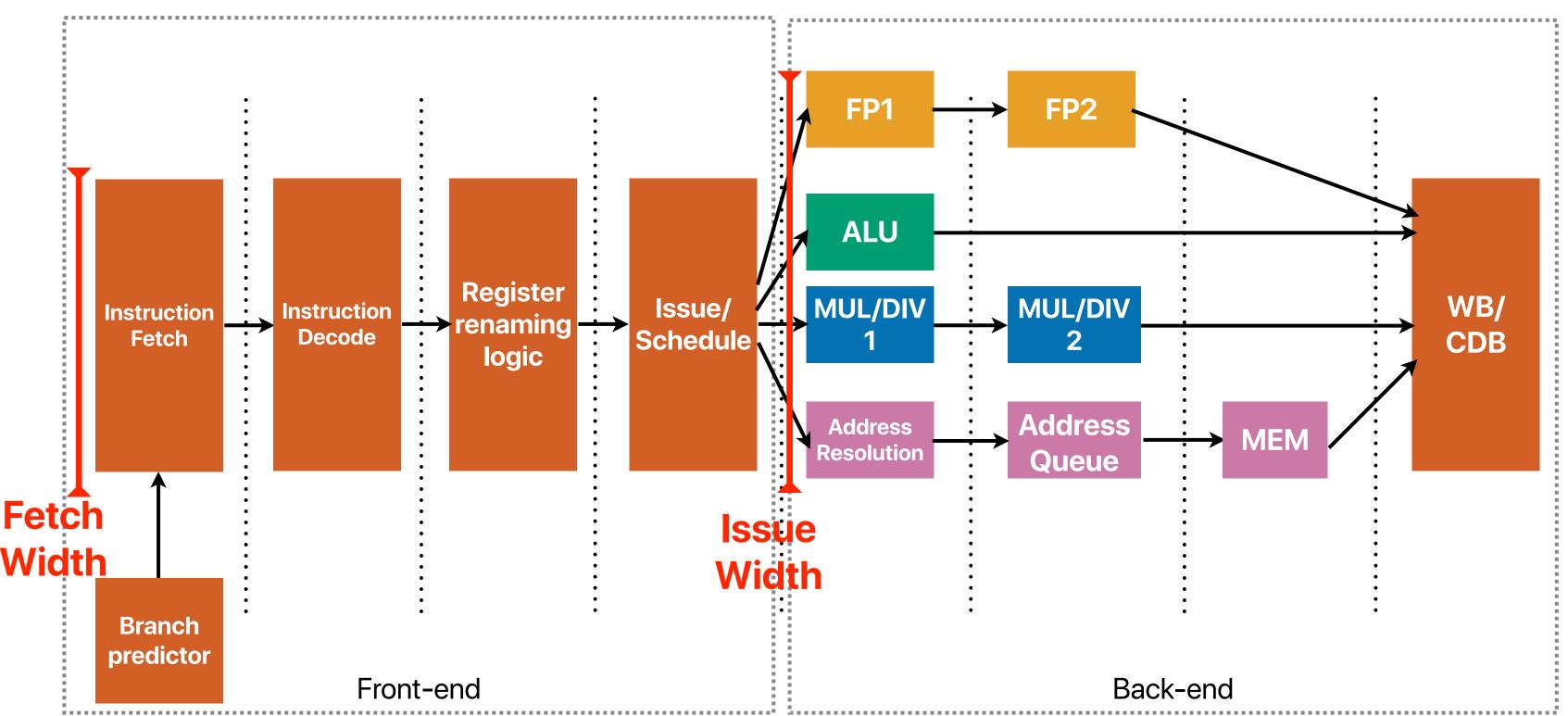

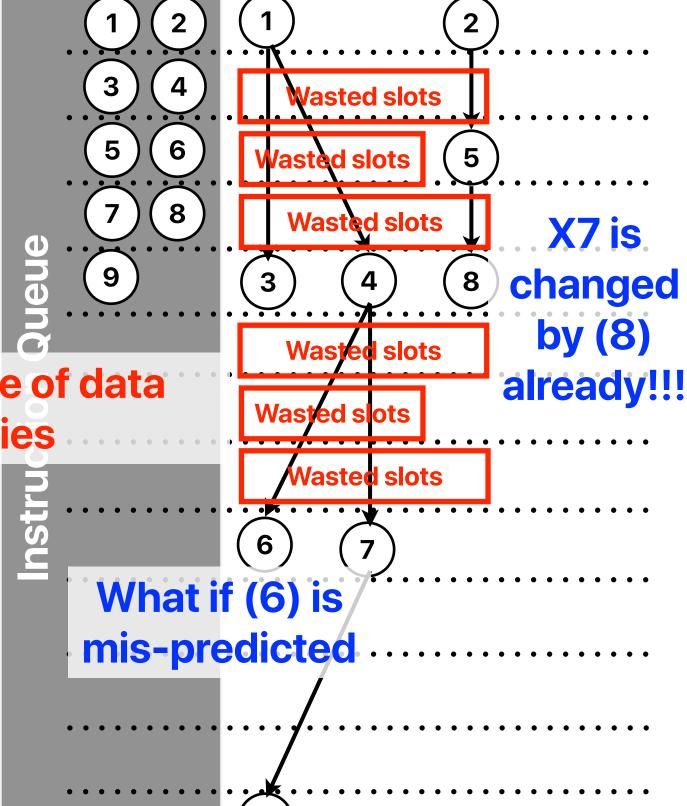

## Recap: Super Scalar Pipeline

#### Superscalar

- Since we have more functional units now, we should fetch/ decode more instructions each cycle so that we can have more instructions to issue!

- Super-scalar: fetch/decode/issue more than one instruction each cycle

- Fetch width: how many instructions can the processor fetch/ decode each cycle

- Issue width: how many instructions can the processor issue each cycle

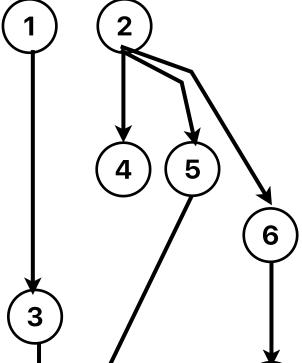

What about "linked list"

#### **Static instructions**

LOOP: ld X10, 8(X10) addi X7, X7, 1 bne X10, X0, LOOP

#### **Dynamic instructions**

- D Id ILP is low because of data

- bne X10 dependencies

- @ ld X10, 8(X10)

- ⑤ addi X7, X7, 1

- bne X10, X0, LOOP

- ① ld X10, 8(X10)

- ® addi X7, X7, 1

- 9 bne X10, X0, LOOP

#### **Team scores**

#### **Outline**

- The Concept of Speculative Execution and Reorder Buffer

- Simultaneous Multithreading

- Chip Multiprocessor

#### In which pipeline stage can we change PCs?

- How many of the following pipeline stages can an instruction change the program counter?

- ① IF

- ② ID

- 3 EXE

- 4 MEM

- ⑤ WB

- A. 1

- B. 2

- C. 3

- D. 4

- E. 5

## In which pipeline stage can we change F

- How many of the following pipeline stages can an instruction change the program counter?

- ① IF

- 2 ID

- 3 EXE

- 4 MEM

- ⑤ WB

- A. 1

- B. 2

- C. 3

- D. 4

- E. 5

## In which pipeline stage can we change PCs?

- How many of the following pipeline stages can an instruction change the program counter?

- page fault, illegal address

- 2 ID unknown instruction

- 3 EXE divide by zero, overflow, underflow, branch mis-prediction

- MEM page fault, illegal address

- ⑤ WB

- A. 1

- B. 2

- C. 3

- D. 4

- E. 5

If you have no idea what's an "exception" and why it's changing the PC — you need to take CS202!

R

- addi X10,X10,8

- ⑤ bne X10,X5,L00P

- 1d X6,0(X10)

- ② add X7,X6,X12

- ® sd X7,0(X10)

- 9 addi X10,X10,8

- 10 bne X10, X5, LOOP

|     | Renamed instruction |      |                   |  |  |  |  |  |  |

|-----|---------------------|------|-------------------|--|--|--|--|--|--|

| 1 - | <del>ld</del>       | P1,  | <del>0(X10)</del> |  |  |  |  |  |  |

| 2 - | add                 | P2,  | P1, X12           |  |  |  |  |  |  |

| 3 - | sd                  | P2,  | <del>0(X10)</del> |  |  |  |  |  |  |

| 4   | addi                | P3,  | X10, 8            |  |  |  |  |  |  |

| 5 - | bne                 | P3,  | X5, LOOP          |  |  |  |  |  |  |

| 6 - | 1d                  | P4,  | 0(P3)             |  |  |  |  |  |  |

| 7 - | add                 | P5,  | P1, X12           |  |  |  |  |  |  |

| 8   | sd                  | -    | 0(P3)             |  |  |  |  |  |  |

| 9 - | addi                | - D/ | P3, 8             |  |  |  |  |  |  |

| 10  | bne                 |      | 0(X10)            |  |  |  |  |  |  |

| 4 |     |     |     |     |        |       |       |      |           |        |       |       |   |

|---|-----|-----|-----|-----|--------|-------|-------|------|-----------|--------|-------|-------|---|

|   | - 1 | AR  | AQ  | MEM | WB     |       |       |      |           |        |       |       |   |

|   | 1.0 | - 1 | 1   | - 1 | - 1    | INT   | WB    |      |           |        |       |       |   |

|   | R   | I   | AR  | AQ  | AQ     | AQ    | AQ    | MEM  | WB        |        |       |       |   |

|   | R   | - 1 | INT | WB  |        |       |       |      |           |        |       |       |   |

|   |     | R   |     |     | BR     | WB_   |       |      | `W        | /hat i | f exc | eptic | n |

|   |     | R   | 1   | X10 | is all | ready | y cha | inge | <b>!!</b> | occi   | urs h | ere?  |   |

|   |     |     | R   | ı   | I      | - 1   | - 1   | ı    | INT       | WB     |       |       |   |

|   |     |     | R   | - 1 | ı      | AR    | AQ    | AQ   | AQ        | AQ     | MEM   | WB    |   |

|   |     |     |     | R   | ı      | - 1   | INT   | WB   |           |        |       |       |   |

|   |     |     |     | R   | I      | - 1   | - 1   | 1    | BR        | WB     |       |       |   |

|            | Physical Register |

|------------|-------------------|

| <b>X</b> 5 |                   |

| X6         | P1                |

| <b>X7</b>  | P5                |

| X10        | Р3                |

| X12        |                   |

|    | Valid | Value | In use |           | Valid | Value | In use |

|----|-------|-------|--------|-----------|-------|-------|--------|

| P1 | 1     |       | 1      | P6        |       |       |        |

| P2 | 1     |       | 1      | <b>P7</b> |       |       |        |

| Р3 | 1     |       | 1      | P8        |       |       |        |

| P4 | 1     |       | 1      | P9        |       |       |        |

| P5 | 1     |       | 1      | P10       |       |       |        |

#### **Speculative Execution**

- The PC can potentially change any time during execution

- Exceptions

- Branches

- Any execution of an instruction before a prior instruction finishes is considered as speculative execution

- Because it's speculative, we need to preserve the capability to restore to the states before it's executed

- Flush incorrectly fetched instructions

- Restore updated register values

- Fetch the right instructions (correct branch target, exception handler)

# Reorder Buffer (ROB)

### Reorder buffer/Commit stage

- Reorder buffer a buffer keep track of the program order of instructions

- Can be combined with IQ or physical registers make either as a circular queue

- Commit stage should the outcome of an instruction be realized

- An instruction can only leave the pipeline if all it's previous are committed

- If any prior instruction failed to commit, the instruction should yield it's ROB entry, restore all it's architectural changes

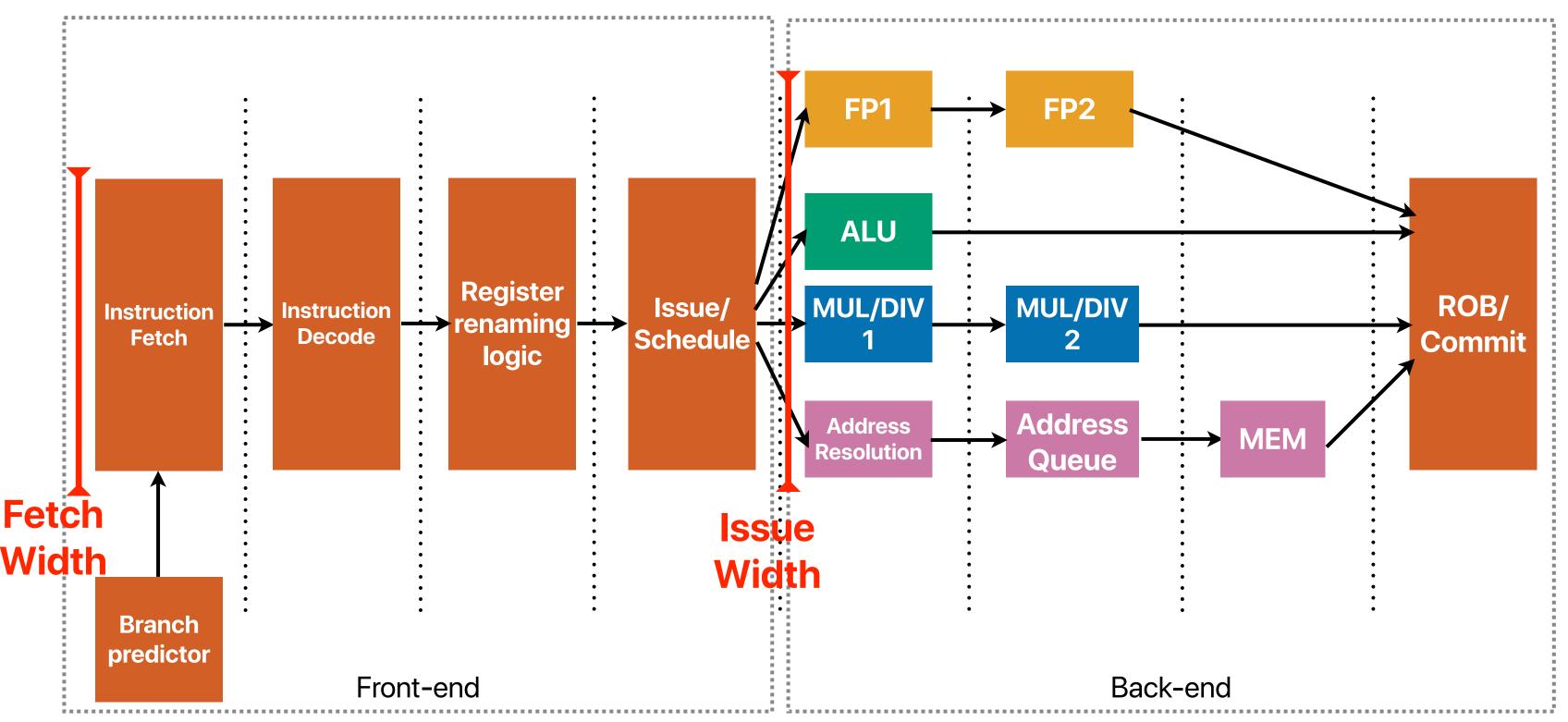

## Pipeline SuperScalar/OoO/ROB

```

① ld X6,0(X10)

```

add X7,X6,X12

- 3 sd X7,0(X10)

- @ addi X10,X10,8

- bne X10,X5,L00P

- © ld X6,0(X10)

- ② add X7,X6,X12

- ® sd X7,0(X10)

- 9 addi X10,X10,8

- 10 bne X10, X5, LOOP

|    | Re         |     |     |     |      |

|----|------------|-----|-----|-----|------|

| 1  | <b>1</b> d | P1, | 0(X | 10) | head |

| 2  | add        | P2, | P1, | X12 | tail |

| 3  |            |     |     |     |      |

| 4  |            |     |     |     |      |

| 5  |            |     |     |     |      |

| 6  |            |     |     |     |      |

| 7  |            |     |     |     |      |

| 8  |            |     |     |     |      |

| 9  |            |     |     |     |      |

| 10 |            |     |     |     |      |

|           | Physical Register |

|-----------|-------------------|

| X5        |                   |

| X6        | P1                |

| <b>X7</b> | P2                |

| X10       |                   |

| X12       |                   |

|    | Valid | Value | In use |           | Valid | Value | In use |

|----|-------|-------|--------|-----------|-------|-------|--------|

| P1 | 0     |       | 1      | P6        |       |       |        |

| P2 | 0     |       | 1      | <b>P7</b> |       |       |        |

| Р3 |       |       |        | P8        |       |       |        |

| P4 |       |       |        | <b>P9</b> |       |       |        |

| P5 |       |       |        | P10       |       |       |        |

X6,0(X10)ld 1 add X7, X6, X12 X7,0(X10)sd addi X10,X10,8

- X10, X5, LOOP bne

- X6,0(X10)ld

- X7, X6, X12 add

- X7,0(X10)sd

- addi X10,X10,8

- 10 X10, X5, LOOP bne

|    | 4.         |     |         |        |

|----|------------|-----|---------|--------|

| 1  | <b>1</b> d | P1, | 0(X10)  | head   |

| 2  | add        | P2, | P1, X12 |        |

| 3  | sd         | P2, | 0(X10)  |        |

| 4  | addi       | P3, | X10, 8  | 💶 tail |

| 5  |            |     |         |        |

| 6  |            |     |         |        |

| 7  |            |     |         |        |

| 8  |            |     |         |        |

| 9  |            |     |         |        |

| 10 |            |     |         |        |

|           | Physical Register |

|-----------|-------------------|

| X5        |                   |

| X6        | P1                |

| <b>X7</b> | P2                |

| X10       | Р3                |

| X12       |                   |

head

|    | Valid | Value | In use |           | Valid | Value | In use |

|----|-------|-------|--------|-----------|-------|-------|--------|

| P1 | 0     |       | 1      | P6        |       |       |        |

| P2 | 0     |       | 1      | <b>P7</b> |       |       |        |

| Р3 | 0     |       | 1      | P8        |       |       |        |

| P4 |       |       |        | <b>P9</b> |       |       |        |

| P5 |       |       |        | P10       |       |       |        |

| 1        | ld   | X6,0(X10)   | R | - 1 | AR  |

|----------|------|-------------|---|-----|-----|

| 2        | add  | X7,X6,X12   | R | - 1 | - 1 |

| 3        | sd   | X7,0(X10)   |   | R   | - 1 |

| 4        | addi | X10,X10,8   |   | R   | - 1 |

| <b>5</b> | bne  | X10,X5,LOOP |   |     | R   |

| 6        | ld   | X6,0(X10)   |   |     | R   |

- ② add X7,X6,X12

- 8 sd X7,0(X10)

- 9 addi X10,X10,8

- 10 bne X10, X5, LOOP

|    | Rer        |     |          |        |

|----|------------|-----|----------|--------|

| 1  | <b>1</b> d | P1, | 0(X10)   | head   |

| 2  | add        | P2, | P1, X12  |        |

| 3  | sd         | P2, | 0(X10)   |        |

| 4  | addi       | P3, | X10, 8   |        |

| 5  | bne        | Р3, | X5, LOOP | _ 4    |

| 6  | <b>1</b> d | P4, | 0(P3)    | 💶 tail |

| 7  |            |     |          |        |

| 8  |            |     |          |        |

| 9  |            |     |          |        |

| 10 |            |     |          |        |

|           | Physical Register |

|-----------|-------------------|

| X5        |                   |

| <b>X6</b> | P1                |

| <b>X7</b> | P2                |

| X10       | Р3                |

| X12       |                   |

|    | Valid | Value | In use |           | Valid | Value | In use |

|----|-------|-------|--------|-----------|-------|-------|--------|

| P1 | 0     |       | 1      | P6        |       |       |        |

| P2 | 0     |       | 1      | <b>P7</b> |       |       |        |

| Р3 | 0     |       | 1      | P8        |       |       |        |

| P4 | 0     |       | 1      | <b>P9</b> |       |       |        |

| P5 |       |       |        | P10       |       |       |        |

|     |      |             |   | <u> </u> |     |     |

|-----|------|-------------|---|----------|-----|-----|

| 1   | ld   | X6,0(X10)   | R | - 1      | AR  | AQ  |

| 2   | add  | X7,X6,X12   | R | - 1      | - 1 | 1   |

| 3   | sd   | X7,0(X10)   |   | R        | - 1 | - 1 |

| 4   | addi | X10,X10,8   |   | R        | 1   | INT |

| (5) | bne  | X10,X5,L00P |   |          | R   | 1   |

| 6   | ld   | X6,0(X10)   |   |          | R   | - 1 |

| 7   | add  | X7,X6,X12   |   |          |     | R   |

| 8   | sd   | X7,0(X10)   |   |          |     | R   |

| 9   | addi | X10,X10,8   |   |          | '   |     |

|   | Rer        | named | instruction |        |

|---|------------|-------|-------------|--------|

| 1 | <b>1</b> d | P1,   | 0(X10)      | head   |

| 2 | add        | P2,   | P1, X12     |        |

| 3 | sd         | P2,   | 0(X10)      |        |

| 4 | addi       | P3,   | X10, 8      |        |

| 5 | bne        | Р3,   | X5, LOOP    |        |

| 6 | <b>1</b> d | P4,   | 0(P3)       |        |

| 7 | add        | P5,   | P1, X12     |        |

| 8 | sd         | P5,   | 0(P3)       | 🚺 tail |

X10, X5, LOOP

10

| Physical Register |    |  |  |  |  |  |  |

|-------------------|----|--|--|--|--|--|--|

| X5                |    |  |  |  |  |  |  |

| X6                | P1 |  |  |  |  |  |  |

| <b>X7</b>         | P5 |  |  |  |  |  |  |

| X10               | Р3 |  |  |  |  |  |  |

| X12               |    |  |  |  |  |  |  |

|    | Valid | Value | In use |           | Valid | Value | In use |

|----|-------|-------|--------|-----------|-------|-------|--------|

| P1 | 0     |       | 1      | P6        |       |       |        |

| P2 | 0     |       | 1      | <b>P7</b> |       |       |        |

| Р3 | 0     |       | 1      | P8        |       |       |        |

| P4 | 0     |       | 1      | <b>P9</b> |       |       |        |

| P5 | 0     |       | 1      | P10       |       |       |        |

| 1  | ld   | X6,0(X10)   | R | ı   | AR  | AQ  | MEM |

|----|------|-------------|---|-----|-----|-----|-----|

| 2  | add  | X7,X6,X12   | R | - 1 | - 1 | - 1 | I   |

| 3  | sd   | X7,0(X10)   |   | R   | 1   | 1   | I   |

| 4  | addi | X10,X10,8   |   | R   | 1   | INT | С   |

| 5  | bne  | X10,X5,L00P |   |     | R   | ı   | 1   |

| 6  | ld   | X6,0(X10)   |   |     | R   |     | 1   |

| 7  | add  | X7,X6,X12   |   |     |     | R   | - 1 |

| 8  | sd   | X7,0(X10)   |   |     |     | R   | 1   |

| 9  | addi | X10,X10,8   |   |     |     |     | R   |

| 10 | bne  | X10,X5,L00P |   |     |     |     | R   |

|    | Ren        | 4   |          |             |

|----|------------|-----|----------|-------------|

| 1  | ld         | P1, | 0(X10)   | head        |

| 2  | add        | P2, | P1, X12  |             |

| 3  | sd         | P2, | 0(X10)   |             |

| 4  | addi       | P3, | X10, 8   |             |

| 5  | bne        | P3, | X5, LOOP |             |

| 6  | <b>1</b> d | P4, | 0(P3)    |             |

| 7  | add        | P5, | P1, X12  |             |

| 8  | sd         | P5, | 0(P3)    |             |

| 9  | addi       | P6, | P3, 8    |             |

| 10 | bne        | P6, | 0(X10)   | <b>tail</b> |

|           | Physical Register |

|-----------|-------------------|

| X5        |                   |

| X6        | P1                |

| <b>X7</b> | P5                |

| X10       | Р3                |

| X12       |                   |

|    | Valid | Value | In use |           | Valid | Value | In use |

|----|-------|-------|--------|-----------|-------|-------|--------|

| P1 | 0     |       | 1      | P6        |       |       |        |

| P2 | 0     |       | 1      | <b>P7</b> |       |       |        |

| Р3 | 1     |       | 1      | P8        |       |       |        |

| P4 | 0     |       | 1      | <b>P9</b> |       |       |        |

| P5 | 0     |       | 1      | P10       |       |       |        |

| 1   | ld   | X6,0(X10)   | R | 1   | AR  | AQ  | MEM | С   |

|-----|------|-------------|---|-----|-----|-----|-----|-----|

| 2   | add  | X7,X6,X12   | R | - 1 | - 1 | - 1 | 1   | - 1 |

| 3   | sd   | X7,0(X10)   |   | R   | 1.0 | 1.0 | ı   | - 1 |

| 4   | addi | X10,X10,8   |   | R   | - 1 | INT | C   | С   |

| (5) | bne  | X10,X5,LOOP | · |     | R   | - 1 | 1   | BR  |

| 6   | ld   | X6,0(X10)   |   |     | R   | - 1 | ı   | AR  |

| 7   | add  | X7,X6,X12   |   |     |     | R   | I   | ı   |

| 8   | sd   | X7,0(X10)   |   |     |     | R   | - 1 | - 1 |

| 9   | addi | X10,X10,8   |   |     |     |     | R   | 1   |

| 10  | bne  | X10,X5,LOOP |   |     |     |     | R   | - 1 |

head

tail

|    | Renamed instruction |     |          |  |  |  |  |  |  |  |

|----|---------------------|-----|----------|--|--|--|--|--|--|--|

| 1  | <b>1</b> d          | P1, | 0(X10)   |  |  |  |  |  |  |  |

| 2  | add                 | P2, | P1, X12  |  |  |  |  |  |  |  |

| 3  | sd                  | P2, | 0(X10)   |  |  |  |  |  |  |  |

| 4  | addi                | P3, | X10, 8   |  |  |  |  |  |  |  |

| 5  | bne                 | Р3, | X5, LOOP |  |  |  |  |  |  |  |

| 6  | <b>1</b> d          | P4, | 0(P3)    |  |  |  |  |  |  |  |

| 7  | add                 | P5, | P1, X12  |  |  |  |  |  |  |  |

| 8  | sd                  | P5, | 0(P3)    |  |  |  |  |  |  |  |

| 9  | addi                | P6, | P3, 8    |  |  |  |  |  |  |  |

| 10 | bne                 | P6, | 0(X10)   |  |  |  |  |  |  |  |

| Physical Register |    |  |  |  |  |  |  |  |

|-------------------|----|--|--|--|--|--|--|--|

| X5                |    |  |  |  |  |  |  |  |

| Х6                | P1 |  |  |  |  |  |  |  |

| <b>X7</b>         | P5 |  |  |  |  |  |  |  |

| X10               | Р3 |  |  |  |  |  |  |  |

| X12               |    |  |  |  |  |  |  |  |

|    | Valid | Value | In use |           | Valid | Value | In use |

|----|-------|-------|--------|-----------|-------|-------|--------|

| P1 | 1     |       | 1      | P6        |       |       |        |

| P2 | 0     |       | 1      | <b>P7</b> |       |       |        |

| Р3 | 1     |       | 1      | P8        |       |       |        |

| P4 | 0     |       | 1      | <b>P9</b> |       |       |        |

| P5 | 0     |       | 1      | P10       |       |       |        |

| 1   | ld   | X6,0(X10)   | R | I | AR  | AQ  | MEM | С   |     |

|-----|------|-------------|---|---|-----|-----|-----|-----|-----|

| 2   | add  | X7,X6,X12   | R | I | 1   | 1   | 1   | 1   | INT |

| 3   | sd   | X7,0(X10)   |   | R | 1   | - 1 | 1.  | - 1 | 1   |

| 4   | addi | X10,X10,8   |   | R | - 1 | INT | С   | С   | С   |

| (5) | bne  | X10,X5,LOOP |   |   | R   | 1   | 1   | BR  | С   |

| 6   | ld   | X6,0(X10)   |   |   | R   | l l | ı   | AR  | AQ  |

| 7   | add  | X7,X6,X12   |   |   |     | R   | ı   | I   | ı   |

| 8   | sd   | X7,0(X10)   |   |   |     | R   | ı   | 1   | ı   |

| 9   | addi | X10,X10,8   |   |   |     |     | R   | 1   | - 1 |

| 10  | bne  | X10,X5,LOOP |   |   |     |     | R   | ı   | ı   |

|     | Rer           | amed | instruction       |             |

|-----|---------------|------|-------------------|-------------|

| 1 - | <del>1d</del> | P1,  | <del>0(X10)</del> | _           |

| 2   | add           | P2,  | P1, X12           | head        |

| 3   | sd            | P2,  | 0(X10)            |             |

| 4   | addi          | Р3,  | X10, 8            |             |

| 5   | bne           | Р3,  | X5, LOOP          |             |

| 6   | <b>1</b> d    | P4,  | 0(P3)             |             |

| 7   | add           | P5,  | P1, X12           |             |

| 8   | sd            | P5,  | 0(P3)             |             |

| 9   | addi          | P6,  | P3, 8             |             |

| 10  | bne           | P6,  | 0(X10)            | <b>tail</b> |

| Physical Register |    |  |  |  |  |  |  |  |  |

|-------------------|----|--|--|--|--|--|--|--|--|

| <b>X5</b>         |    |  |  |  |  |  |  |  |  |

| X6                | P1 |  |  |  |  |  |  |  |  |

| <b>X7</b>         | P5 |  |  |  |  |  |  |  |  |

| X10               | Р3 |  |  |  |  |  |  |  |  |

| X12               |    |  |  |  |  |  |  |  |  |

|    | Valid | Value | In use |           | Valid | Value | In use |

|----|-------|-------|--------|-----------|-------|-------|--------|

| P1 | 1     |       | 1      | P6        |       |       |        |

| P2 | 0     |       | 1      | <b>P7</b> |       |       |        |

| Р3 | 1     |       | 1      | P8        |       |       |        |

| P4 | 0     |       | 1      | P9        |       |       |        |

| P5 | 0     |       | 1      | P10       |       |       |        |

|    |      | <del></del> |   |     |     |     |     |     |     |     |

|----|------|-------------|---|-----|-----|-----|-----|-----|-----|-----|

| 1  | ld   | X6,0(X10)   | R | - 1 | AR  | AQ  | MEM | С   |     |     |

| 2  | add  | X7,X6,X12   | R | I   | - 1 | 1   | - 1 | 1   | INT | С   |

| 3  | sd   | X7,0(X10)   |   | R   | - 1 | I   | ı   | - 1 | I   | - 1 |

| 4  | addi | X10,X10,8   |   | R   | - 1 | INT | С   | С   | С   | С   |

| 5  | bne  | X10,X5,LOOP |   |     | R   | 1   | 1   | BR  | С   | С   |

| 6  | ld   | X6,0(X10)   |   |     | R   | ı   | 1   | AR  | AQ  | MEM |

| 7  | add  | X7,X6,X12   |   |     |     | R   | - 1 | - I | 1   | - 1 |

| 8  | sd   | X7,0(X10)   |   |     |     | R   | ı   | - 1 | ı   | - 1 |

| 9  | addi | X10,X10,8   |   |     |     |     | R   | - 1 | 1   | INT |

| 10 | bne  | X10,X5,LOOP |   |     |     |     | R   | 1   | ı   | - 1 |

|    |      |             |   |     |     |     |     |     |     |     |

|     | Rer           | named | instruction       |             |

|-----|---------------|-------|-------------------|-------------|

| 1 - | <del>ld</del> | P1,   | <del>0(X10)</del> | 1           |

| 2   | add           | P2,   | P1, X12           | head        |

| 3   | sd            | P2,   | 0(X10)            |             |

| 4   | addi          | Р3,   | X10, 8            |             |

| 5   | bne           | Р3,   | X5, LOOP          |             |

| 6   | ld            | P4,   | 0(P3)             |             |

| 7   | add           | P5,   | P1, X12           |             |

| 8   | sd            | P5,   | 0(P3)             |             |

| 9   | addi          | P6,   | P3, 8             |             |

| 10  | bne           | P6,   | 0(X10)            | <b>tail</b> |

|           | Physical Register |

|-----------|-------------------|

| <b>X5</b> |                   |

| Х6        | P1                |

| <b>X7</b> | P5                |

| X10       | Р3                |

| X12       |                   |

|    | Valid | Value | In use |           | Valid | Value | In use |

|----|-------|-------|--------|-----------|-------|-------|--------|

| P1 | 1     |       | 1      | P6        |       |       |        |

| P2 | 1     |       | 1      | <b>P7</b> |       |       |        |

| Р3 | 1     |       | 1      | P8        |       |       |        |

| P4 | 0     |       | 1      | <b>P9</b> |       |       |        |

| P5 | 0     |       | 1      | P10       |       |       |        |

|     | Rer           | named | instruction       |             |

|-----|---------------|-------|-------------------|-------------|

| 1 - | <del>ld</del> | P1,   | <del>0(X10)</del> | _           |

| 2 - | add           | P2,   | P1, X12           |             |

| 3   | sd            | P2,   | 0(X10)            | head        |

| 4   | addi          | Р3,   | X10, 8            |             |

| 5   | bne           | Р3,   | X5, LOOP          |             |

| 6   | ld            | P4,   | 0(P3)             |             |

| 7   | add           | P5,   | P1, X12           |             |

| 8   | sd            | P5,   | 0(P3)             |             |

| 9   | addi          | P6,   | P3, 8             |             |

| 10  | bne           | P6,   | 0(X10)            | <b>tail</b> |

|           | Physical Register |

|-----------|-------------------|

| X5        |                   |

| Х6        | P1                |

| <b>X7</b> | P5                |

| X10       | Р3                |

| X12       |                   |

|    | Valid | Value | In use |           | Valid | Value | In use |

|----|-------|-------|--------|-----------|-------|-------|--------|

| P1 | 1     |       | 1      | P6        |       |       |        |

| P2 | 1     |       | 1      | <b>P7</b> |       |       |        |

| Р3 | 1     |       | 1      | P8        |       |       |        |

| P4 | 1     |       | 1      | <b>P9</b> |       |       |        |

| P5 | 0     |       | 1      | P10       |       |       |        |

| 4    addi X10, X10, 8          R    I    INT    C    C    C    C    C    C                |     |      |             |   |     |     |     |     |     |     |     |     |     |

|-------------------------------------------------------------------------------------------|-----|------|-------------|---|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| <ul> <li>③ sd X7,0(X10)</li> <li>④ addi X10,X10,8</li> <li>R I INT C C C C C C</li> </ul> | 1   | ld   | X6,0(X10)   | R | - 1 | AR  | AQ  | MEM | С   |     |     |     |     |

| @ addi X10,X10,8 R I INT C C C C C                                                        | 2   | add  | X7,X6,X12   | R | - 1 | 1   | 1.  | 1   | 1   | INT | С   |     |     |

|                                                                                           | 3   | sd   | X7,0(X10)   |   | R   | ı   | - 1 | 1   | ı   | I   | I   | AR  | AQ  |

| s bne X10, X5, LOOP R I BR C C C C                                                        | 4   | addi | X10,X10,8   |   | R   | - 1 | INT | С   | C   | С   | С   | С   | С   |

|                                                                                           | (5) | bne  | X10,X5,LOOP |   |     | R   | 1.0 | 1   | BR  | С   | С   | С   | С   |

| (a) 1d X6,0(X10) R I I AR AQ MEM C C                                                      | 6   | ld   | X6,0(X10)   |   |     | R   | - 1 | ı   | AR  | AQ  | MEM | С   | С   |

| add X7, X6, X12 R I I I I I I I I I I I I I I I I I I I                                   | 7   | add  | X7,X6,X12   |   |     |     | R   | ı   | - 1 | - 1 | ı   | - 1 | INT |

| <pre>     sd X7,0(X10)     R    I    I    I    I    I </pre>                              | 8   | sd   | X7,0(X10)   |   |     |     | R   | ı   | ı   | - 1 | - 1 | - 1 | l l |

| <pre>     addi X10,X10,8     R    I    I    INT    C    C </pre>                          | 9   | addi | X10,X10,8   |   |     |     |     | R   | L   | - 1 | INT | С   | С   |

| ① bne X10,X5,L00P R I I I BR                                                              | 10  | bne  | X10,X5,LOOP |   |     |     |     | R   | - 1 | - 1 | 1   | - 1 | BR  |

|     | Rer           | named | instruction       |             |

|-----|---------------|-------|-------------------|-------------|

| 1 - | <del>1d</del> | P1,   | <del>0(X10)</del> | -           |

| 2 - | add           | P2,   | P1, X12           | <b>-</b> 4  |

| 3   | sd            | P2,   | 0(X10)            | head        |

| 4   | addi          | Р3,   | X10, 8            |             |

| 5   | bne           | Р3,   | X5, LOOP          |             |

| 6   | <b>1</b> d    | P4,   | 0(P3)             |             |

| 7   | add           | P5,   | P1, X12           |             |

| 8   | sd            | P5,   | 0(P3)             |             |

| 9   | addi          | P6,   | P3, 8             | _ 4         |

| 10  | bne           | P6,   | 0(X10)            | <b>tail</b> |

|           | Physical Register |

|-----------|-------------------|

| <b>X5</b> |                   |

| <b>X6</b> | P1                |

| <b>X7</b> | P5                |

| X10       | Р3                |

| X12       |                   |

|    | Valid | Value | In use |           | Valid | Value | In use |

|----|-------|-------|--------|-----------|-------|-------|--------|

| P1 | 1     |       | 1      | P6        |       |       |        |

| P2 | 1     |       | 1      | <b>P7</b> |       |       |        |

| Р3 | 1     |       | 1      | P8        |       |       |        |

| P4 | 1     |       | 1      | <b>P9</b> |       |       |        |

| P5 | 0     |       | 1      | P10       |       |       |        |

| 1        | ld   | X6,0(X10)   | R | - 1 | AR  | AQ  | MEM | С   |     |     |     |     |     |

|----------|------|-------------|---|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 2        | add  | X7,X6,X12   | R | - 1 | - 1 | - 1 | 1   | 1   | INT | С   |     |     |     |

| 3        | sd   | X7,0(X10)   |   | R   |     | - 1 | ı   | - 1 | - 1 | 1   | AR  | AQ  | MEM |

| 4        | addi | X10,X10,8   |   | R   | ı   | INT | С   | С   | С   | С   | С   | С   | С   |

| <b>5</b> | bne  | X10,X5,L00P |   |     | R   | - 1 | 1   | BR  | С   | С   | С   | С   | С   |

| 6        | ld   | X6,0(X10)   |   |     | R   | - 1 | 1   | AR  | AQ  | MEM | С   | С   | C   |

| 7        | add  | X7,X6,X12   |   |     |     | R   | ı   | - 1 | - 1 | ı   | - 1 | INT | С   |

| 8        | sd   | X7,0(X10)   |   |     |     | R   | ı   | - 1 | 1   | 1.0 | - 1 | 1.0 | 1   |

| 9        | addi | X10,X10,8   |   |     |     |     | R   | - 1 | - 1 | INT | С   | С   | С   |

| 10       | bne  | X10,X5,L00P |   |     |     |     | R   | 1   | - 1 | I   | - 1 | BR  | С   |

|          |      |             |   |     |     |     |     |     |     |     |     |     |     |

|     | Ren           | amed | instruction       |             |

|-----|---------------|------|-------------------|-------------|

| 1 - | <del>1d</del> | P1,  | <del>0(X10)</del> | _           |

| 2 - | add           | P2,  | P1, X12           |             |

| 3   | sd            | P2,  | 0(X10)            | head        |

| 4   | addi          | P3,  | X10, 8            |             |

| 5   | bne           | P3,  | X5, LOOP          |             |

| 6   | <b>1</b> d    | P4,  | 0(P3)             |             |

| 7   | add           | P5,  | P1, X12           |             |

| 8   | sd            | P5,  | 0(P3)             |             |

| 9   | addi          | P6,  | P3, 8             |             |

| 10  | bne           | P6,  | 0(X10)            | <b>tail</b> |

|           | Physical Register |

|-----------|-------------------|

| X5        |                   |

| X6        | P1                |

| <b>X7</b> | P5                |

| X10       | Р3                |

| X12       |                   |

|    | Valid | Value | In use |           | Valid | Value | In use |

|----|-------|-------|--------|-----------|-------|-------|--------|

| P1 | 1     |       | 1      | P6        |       |       |        |

| P2 | 1     |       | 1      | <b>P7</b> |       |       |        |

| Р3 | 1     |       | 1      | P8        |       |       |        |

| P4 | 1     |       | 1      | <b>P9</b> |       |       |        |

| P5 | 1     |       | 1      | P10       |       |       |        |

|     |      |             |   | <b>M</b> |     |     |     |     |     |     |    |     |     |    |

|-----|------|-------------|---|----------|-----|-----|-----|-----|-----|-----|----|-----|-----|----|

| 1   | ld   | X6,0(X10)   | R | 1        | AR  | AQ  | MEM | С   |     |     |    |     |     |    |

| 2   | add  | X7,X6,X12   | R | I        | - 1 | - 1 | - 1 | - 1 | INT | С   |    |     |     |    |

| 3   | sd   | X7,0(X10)   |   | R        | 1.  | 1.  | 1   | - 1 | 1.0 | 1   | AR | AQ  | MEM | C  |

| 4   | addi | X10,X10,8   |   | R        | 1.  | INT | С   | С   | С   | С   | С  | C   | C   | C  |

| (5) | bne  | X10,X5,LOOP |   |          | R   | 1   | - 1 | BR  | С   | С   | С  | С   | С   | С  |

| 6   | ld   | X6,0(X10)   |   |          | R   | 1   | ı   | AR  | AQ  | MEM | С  | С   | C   | C  |

| 7   | add  | X7,X6,X12   |   |          |     | R   | - 1 | ı   | ı   | ı   | ı  | INT | С   | С  |

| 8   | sd   | X7,0(X10)   |   |          |     | R   | - 1 | - 1 | - 1 | - 1 | I  | - 1 | 1   | AF |

| 9   | addi | X10,X10,8   |   |          |     |     | R   | - 1 | - 1 | INT | С  | С   | С   | С  |

| 10  | bne  | X10,X5,LOOP |   |          |     |     | R   | 1   | 1   | ı   | ı  | BR  | С   | С  |

|     | Ren            | amed | instruction       |   |      |

|-----|----------------|------|-------------------|---|------|

| 1 - | <del>1d</del>  | P1,  | <del>0(X10)</del> | _ |      |

| 2 - | add            | P2,  | P1, X12           | _ |      |

| 3 - | sd             | P2,  | <del>0(X10)</del> | _ |      |

| 4 - | addi           | P3,  | X10, 8            | _ |      |

| 5 - | bno            | D3,  | X5, LOOP          | _ |      |

| 6 - | <del>1</del> d | P4,  | 0(P3)             | _ |      |

| 7 - | add            | P5,  | P1, X12           | - |      |

| 8   | sd             | P5,  | 0(P3)             |   | head |

| 9   | addi           | P6,  | P3, 8             |   |      |

| 10  | bne            | P6,  | 0(X10)            |   | tail |

|           | Physical Register |

|-----------|-------------------|

| <b>X5</b> |                   |

| X6        | P1                |

| <b>X7</b> | P5                |

| X10       | Р3                |

| X12       |                   |

|    | Valid | Value | In use |           | Valid | Value | In use |

|----|-------|-------|--------|-----------|-------|-------|--------|

| P1 | 1     |       | 1      | P6        |       |       |        |

| P2 | 1     |       | 1      | <b>P7</b> |       |       |        |

| Р3 | 1     |       | 1      | P8        |       |       |        |

| P4 | 1     |       | 1      | P9        |       |       |        |

| P5 | 1     |       | 1      | P10       |       |       |        |

INT

C

AQ

C

C

MEM

INT

AR

C

C

C

AQ

C

C

INT

BR

MEM

C

C

C

C

C

C

C

C

C

AR

C

AQ

C

C

| 7 | add | X7,X6,X12 |

|---|-----|-----------|

| 8 | sd  | X7,0(X10) |

- 9 addi X10,X10,8

- ① bne X10, X5, LOOP

|     | Rer           | named | instruction       |             |  |

|-----|---------------|-------|-------------------|-------------|--|

| 1 - | <del>ld</del> | P1,   | <del>0(X10)</del> | _           |  |

| 2 - | add           | P2,   | D1, X12           |             |  |

| 3 - | sd            | P2,   | <del>0(X10)</del> | -           |  |

| 4 - | addi          | P3,   | X10, 8            | -           |  |

| 5 - | brie          | P3,   | X5, LOOP          | _           |  |

| 6 - | 1d            | P4,   | <del>0(P3)</del>  | -           |  |

| 7 - | add           | P5,   | P1, X12           |             |  |

| 8   | sd            | P5,   | 0(P3)             | head        |  |

| 9   | addi          | Р6,   | P3, 8             |             |  |

| 10  | bne           | P6,   | 0(X10)            | <b>tail</b> |  |

|            | Physical Register |

|------------|-------------------|

| <b>X</b> 5 |                   |

| X6         | P1                |

| <b>X7</b>  | P5                |

| X10        | Р3                |

| X12        |                   |

R

R

R

R

|    | Valid | Value | In use |           | Valid | Value | In use |

|----|-------|-------|--------|-----------|-------|-------|--------|

| P1 | 1     |       | 1      | P6        |       |       |        |

| P2 | 1     |       | 1      | <b>P7</b> |       |       |        |

| Р3 | 1     |       | 1      | P8        |       |       |        |

| P4 | 1     |       | 1      | <b>P9</b> |       |       |        |

| P5 | 1     |       | 1      | P10       |       |       |        |

|     | Ren           |     |                   |             |

|-----|---------------|-----|-------------------|-------------|

| 1 - | <del>1d</del> | P1, | <del>0(X10)</del> | -           |

| 2 _ | add           | P2, | P1, X12           |             |

| 3 - | sd            | P2, | 0(X10)            | _           |

| 4 - | addi          | P3, | V40 0             | -           |

| 5 - | biie          | P3, | X5, LOOP          | _           |

| 6 - | 7 4           | D/  | 0(02)             |             |

| 7 - |               | DE. | D1 V12            |             |

|     | add           |     | 0 ( 70 )          | 4 bood      |

| 8   | sd            | P5, | 0(P3)             | head        |

| 9   | addi          | P6, | P3, 8             |             |

| 10  | bne           | P6, | 0(X10)            | <b>tail</b> |

|           | Physical Register |

|-----------|-------------------|

| <b>X5</b> |                   |

| X6        | P1                |

| <b>X7</b> | P5                |

| X10       | Р3                |

| X12       |                   |

|    | Valid | Value | In use |           | Valid | Value | In use |

|----|-------|-------|--------|-----------|-------|-------|--------|

| P1 | 1     |       | 1      | P6        |       |       |        |

| P2 | 1     |       | 1      | <b>P7</b> |       |       |        |

| Р3 | 1     |       | 1      | P8        |       |       |        |

| P4 | 1     |       | 1      | <b>P9</b> |       |       |        |

| P5 | 1     |       | 1      | P10       |       |       |        |

| 1 | ld   | X6,0(X10)   |  |

|---|------|-------------|--|

| 2 | add  | X7,X6,X12   |  |

| 3 | sd   | X7,0(X10)   |  |

| 4 | addi | X10,X10,8   |  |

| 5 | bne  | X10,X5,LOOP |  |

| 6 | ld   | X6,0(X10)   |  |

| 7 | add  | X7,X6,X12   |  |

| 8 | sd   | X7,0(X10)   |  |

| _ | •    |             |  |

| ) | addi | X10, X10, 8 |

|---|------|-------------|

|   | bne  | X10,X5,LOOP |

| bne X10,X5,L00P  |                     |                   |  |  |  |  |  |  |

|------------------|---------------------|-------------------|--|--|--|--|--|--|

|                  | Rename              | d instruction     |  |  |  |  |  |  |

| 1 - 1            | <del>d P1,</del>    | <del>0(X10)</del> |  |  |  |  |  |  |

| 2                | dd P2,              | P1, X12           |  |  |  |  |  |  |

| 3 30             | d P2,               | <del>0(X10)</del> |  |  |  |  |  |  |

| 4   a            | <del>ddi P3</del> , | , X10, 8          |  |  |  |  |  |  |

| 5 <del>b</del> ı | ie P3,              | , X5, L00F        |  |  |  |  |  |  |

| 6 -1             | <del>1 P4,</del>    | 0(P3)             |  |  |  |  |  |  |

| 7 <del>- a</del> | dd P5,              | P1, X12           |  |  |  |  |  |  |

| 8                | <del>P5,</del>      | 0(P3)             |  |  |  |  |  |  |

| 9                | ddi P6,             | D3/ 8             |  |  |  |  |  |  |

| 10 by            | 20 D6               | 9(Y19)            |  |  |  |  |  |  |

| 1. | AR  | AQ  | MEM | С   |     |     |     |     |     |

|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 10 | 1.1 | 1.0 | - 1 | 100 | INT | С   |     |     |     |

| R  | 1.  | - 1 | 1   | ı   | I   | ı   | AR  | AQ  | MEM |

| R  | 1.0 | INT | С   | С   | C   | С   | С   | C   | C   |

|    | R   | 1   | - 1 | BR  | С   | С   | С   | С   | С   |

|    | R   | ı   | 1   | AR  | AQ  | MEM | WB  | С   | С   |

|    |     | R   | - 1 | I   | - 1 | ı   | - 1 | INT | С   |

|    |     | R   | 1   | ı   | - 1 | - 1 | - 1 | - 1 | ı   |

|    |     |     | R   | 1   | - 1 | INT | С   | C   | С   |

|    |     |     |     |     |     |     |     | -   |     |

| Physical Register |    |  |  |  |  |  |

|-------------------|----|--|--|--|--|--|

| <b>X5</b>         |    |  |  |  |  |  |

| X6                | P1 |  |  |  |  |  |

| <b>X7</b>         | P5 |  |  |  |  |  |

| X10               | Р3 |  |  |  |  |  |

| X12               |    |  |  |  |  |  |

teilad

|    | Valid | Value | In use |     | Valid | Value | In use |

|----|-------|-------|--------|-----|-------|-------|--------|

| P1 | 1     |       | 1      | P6  |       |       |        |

| P2 | 1     |       | 1      | P7  |       |       |        |

| Р3 | 1     |       | 1      | P8  |       |       |        |

| P4 | 1     |       | 1      | P9  |       |       |        |

| P5 | 1     |       | 1      | P10 |       |       |        |

AR

AQ

MEM

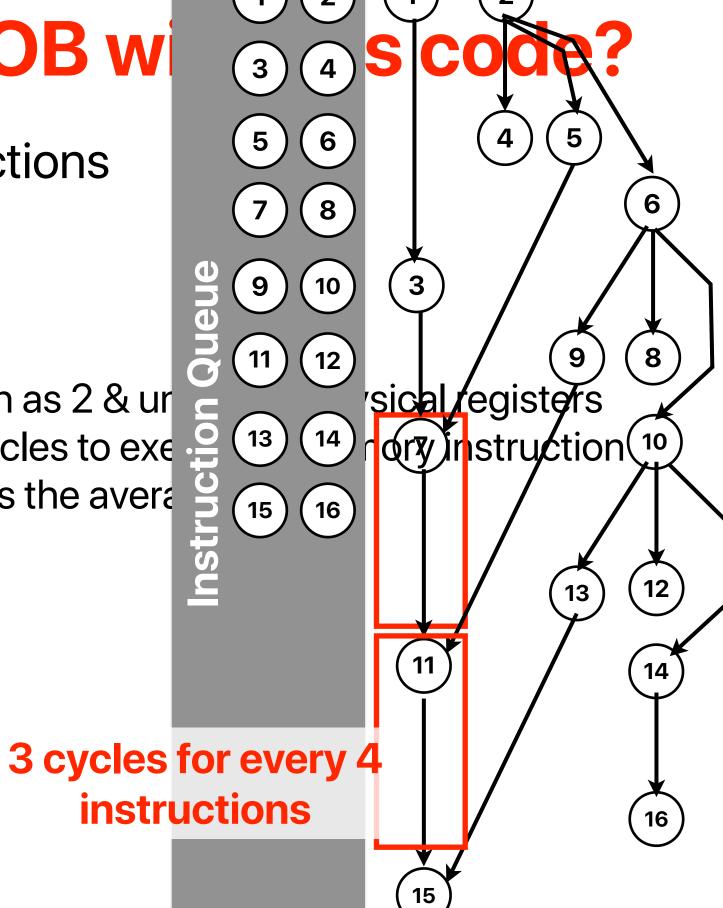

#### How good is SS/OoO/ROB with this code?

Consider the following dynamic instructions

```

1d X1, 0(X10)

addi X10, X10, 8

add X20, X20, X1

bne X10, X2, LOOP

ld X1, 0(X10)

addi X10, X10, 8

add X20, X20, X1

bne X10, X2, LOOP

```

Assume a superscalar processor with **issue width as 2** & unlimited physical registers that can fetch up to 2 instructions per cycle, 3 cycles to execute a memory instruction how many cycles it takes to issue all instructions?

- A. 1

- B. 3

- C. 5

- D. 7

- E. 9

## How good is SS/OoO/ROB with this co

- Consider the following dynamic instructions

- ① ld X1, 0(X10)

- ② addi X10, X10, 8

- add X20, X20, X1

- bne X10, X2, L00P

- ⑤ ld X1, 0(X10)

- ⊚ addi X10, X10, 8

- add X20, X20, X1

- bne X10, X2, L00P

Assume a superscalar processor with **issue width as 2** & unlimited physical registers that can fetch up to 2 instructions per cycle, 3 cycles to execute a memory instruction how many cycles it takes to issue all instructions?

- A. 1

- B. 3

- C. 5

- D. 7

- E. 9

How good is SS/OoO/ROB with this code?

- Consider the following dynamic instructions

- ① ld X1, 0(X10)

- ② addi X10, X10, 8

- 3 add X20, X20, X1

- bne X10, X2, L00P

- ⑤ ld X1, 0(X10)

- addi X10, X10, 8

- add X20, X20, X1

- ® bne X10, X2, LOOP

Assume a superscalar processor with **issue width as 2** & unlimited physical registers that can fetch up to 2 instructions per cycle, 3 cycles to execute a memory instruction how many cycles it takes to issue all instructions?

- A. 1

- B. 3

- C. 5

- D. 7

- E. 9

# A feature of speculative execution

#### Putting it all together

- How many of the following would happen given the modern processor microarchitecture?

- ① The branch predictor will predict not taken for branch A

- ② The cache may contain the content of array2[array1[16] \* 512];

- @ temp can potentially become the value of array2[array1[16] \* 512];

- The program will raise an exception

40

#### Putting it all together

- How many of the following would happen given the modern processor microarchitecture?

- 1 The branch predictor will predict not taken for branch A

- ② The cache may contain the content of array2[array1[16] \* 512];

- ③ temp can potentially become the value of array2[array1[16] \* 512];

- The program will raise an exception

41

#### Putting it all together

- How many of the following would happen given the modern processor microarchitecture?

- The branch predictor will predict not taken for branch A —very likely

- The cache may contain the content of array2[array1[16] \* 512]; The cache may contain the content of array2[array1[16] \* 512];

```

512]; — not really, as x < array1_size

```

The program will raise an exception

```

A. O — maybe?

```

B. 1

C. 2

D. 3

E. 4

```

unsigned int array1_size = 16;

uint8_t array1[160] = { 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15, 16, 260};

uint8_t array2[256 * 512];

void bar(size_t x) {

if (x < array1_size) { // Branch A: Taken if the statement is not going to be executed.

temp &= array2[array1[x] * 512];

}

}

void foo(size_t x) {

int i = 0, j=0;

for(j=0;j<10000;j++)

bar(rand()%17);

}</pre>

```

## Spectre and meltdown

#### What happen when mis-speculation detected

- Exceptions and incorrect branch prediction can cause "rollback" of transient instructions

- Old register states are preserved, can be restored

- Memory writes are buffered, can be discarded

- Cache modifications are not restored!

#### Speculative execution on the following code

- Execution without speculation is safe

- CPU will never read array1[x] for any  $x \ge array1\_size$

- if (x < array1\_size)

y = array2[array1[x] \* 256];</pre>

- Execution with speculation can be exploited

- Attacker sets up some conditions

- train branch predictor to assume 'if' is likely true

- make array1\_size and array2[] uncached

- Invokes code with out-of-bounds x such that array1[x] is a secret

- Processor recognizes its error when array1\_size arrives, restores its architectural state, and proceeds with 'if' false

- Attacker detects cache change (e.g. basic FLUSH+RELOAD or EVICT+RELOAD)

- E.g. next read to array2[i\*256] will be fast i=array[x] since this got cached

#### How good is SS/OoO/ROB with this code?

- Consider the following dynamic instructions

- ① ld X1, 0(X10)

- ② addi X10, X10, 8

- 3 add X20, X20, X1

- bne X10, X2, L00P

Assume a superscalar processor with issue width as 2 & unlimited physical registers that can fetch up to 4 instructions per cycle, 3 cycles to execute a memory instruction and the loop will execute for 10,000 times, what's the average CPI?

- A. 0.5

- B. 0.75

- C. 1

- D. 1.25

- E. 1.5

## How good is SS/OoO/ROB with this co

- Consider the following dynamic instructions

- ① ld X1, 0(X10)

- ② addi X10, X10, 8

- 3 add X20, X20, X1

- bne X10, X2, L00P

Assume a superscalar processor with issue width as 2 & unlimited physical registers that can fetch up to 4 instructions per cycle, 3 cycles to execute a memory instruction and the loop will execute for 10,000 times, what's the average CPI?

- A. 0.5

- B. 0.75

- C. 1

- D. 1.25

- E. 1.5

#### How good is SS/OoO/ROB w

- Consider the following dynamic instructions

- ① ld X1, 0(X10)

- ② addi X10, X10, 8

- 3 add X20, X20, X1

- bne X10, X2, L00P

Assume a superscalar processor with issue width as 2 & ur that can fetch up to 4 instructions per cycle, 3 cycles to exe and the loop will execute for 10,000 times, what's the average

X1, 0(X10)

X10, X2, LOOP

- A. 0.5

- B. 0.75

- C. 1

- D. 1.25

- E. 1.5

② addi X10, X10, 8

③ add X20, X20, X1

④ bne X10, X2, LOOP

⑤ ld X1, 0(X10)

⑥ addi X10, X10, 8

⑦ add X20, X20, X1

⑥ bne X10, X2, LOOP

⑨ ld X1, 0(X10)

⑥ addi X10, X10, 8

① addi X10, X10, 8

① addi X20, X20, X1

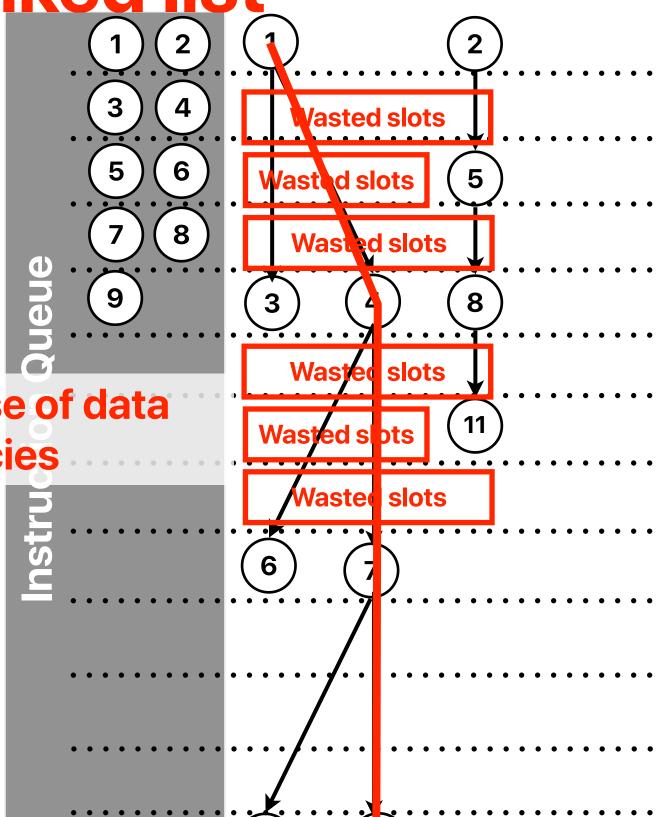

What about "linked list"

#### **Static instructions**

LOOP: ld X10, 8(X10) addi X7, X7, 1 bne X10, X0, LOOP

#### **Dynamic instructions**

- 1 ld ILP is low because of data

- bne X10 dependencies

- @ ld X10, 8(X10)

- s addi X7, X7, 1

- bne X10, X0, L00P

- ① ld X10, 8(X10)

- ® addi X7, X7, 1

- 9 bne X10, X0, LOOP

**5**

10

#### Demo: ILP within a program

perf is a tool that captures performance counters of your processors and can generate results like branch mis-prediction rate, cache miss rates and ILP.

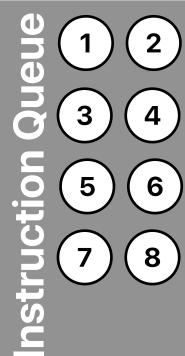

# Simultaneous multithreading

#### Simultaneous multithreading

- The processor can schedule instructions from different threads/processes/programs

- Fetch instructions from different threads/processes to fill the not utilized part of pipeline

- Exploit "thread level parallelism" (TLP) to solve the problem of insufficient ILP in a single thread

- You need to create an illusion of multiple processors for OSs

#### Simultaneous multithreading

```

X10, 8(X10)

① ld

ld

X1, 0(X10)

② addi X7, X7, 1

addi X10, X10, 8

X20, X20, X1

add

X10, 8(X10)

4 1d

6

5

X10, X2, LOOP

bne

⑤ addi X7, X7, 1

X1, 0(X10)

ld

bne X10, X0, LOOP

addi X10, X10, 8

ld X10, 8(X10)

10

add

X20, X20, X1

3

® addi X7, X7, 1

X10, X2, LOOP

bne

bne

X10, X0, LOOP

8)

3

X1, 0(X10)

ld

addi X10, X10, 8

add

X20, X20, X1

bne X10, X2, LOOP

53

```

#### Architectural support for simultaneous multithreading

- To create an illusion of a multi-core processor and allow the core to run instructions from multiple threads concurrently, how many of the following units in the processor must be duplicated/extended?

- ① Program counter

- ② Register mapping tables

- ③ Physical registers

- 4 ALUs

- ⑤ Data cache

- ® Reorder buffer/Instruction Queue

- A. 2

- B. 3

- C. 4

- D. 5

- E. 6

#### Architectural support for simultaneous multithrea

- To create an illusion of a multi-core processor and allow the core to run instructions from multiple threads concurrently, how many of the following units in the processor must be duplicated/extended?

- ① Program counter

- ② Register mapping tables

- ③ Physical registers

- 4 ALUs

- ⑤ Data cache

- ® Reorder buffer/Instruction Queue

- A. 2

- B. 3

- C. 4

- D. 5

- E. 6

#### Architectural support for simultaneous multithreading

- To create an illusion of a multi-core processor and allow the core to run instructions from multiple threads concurrently, how many of the following units in the processor must be duplicated/extended?

- ① Program counter you need to have one for each context

- 2 Register mapping tables you need to have one for each context

- 4 ALUsyou can share

- Data cacheyou can share

- © Reorder buffer/Instruction Queue

- A. 2 you need to indicate which context the instruction is from

- B. 3

- C. 4

- D. 5

- E. 6

SuperScalar Processor w/ ROB Fetch/decode instruction physical Renaming **Unresolved** X1 register # **Branch** logic **Physical** Register Registers mapping table Instruction -Queue Floating-Floating-Address Integer **Branch Point Adder Point Mul/Div** Resolution **ALU Store** Load Queue Queue Memory Data Address

SMT SuperScalar Processor w/ ROB physical register # Fetch/ PC #1 → Register decode Renaming PC #2 mapping table #1 instruction logic Physical physical re Registers Register **Instruction** mapping table #2 Queue Floating-**Address** Floating-Integer **Branch Point Adder Point Mul/Div** Resolution **ALU Store** Load Queue Queue **Memory** Data Address

#### **SMT**

- How many of the following about SMT are correct?

- ① SMT makes processors with deep pipelines more tolerable to mis-predicted branches

- ② SMT can improve the throughput of a single-threaded application

- ③ SMT processors can better utilize hardware during cache misses comparing with superscalar processors with the same issue width

- MT processors can have higher cache miss rates comparing with superscalar processors with the same cache sizes when executing the same set of applications.

- A. 0

- B. 1

- C. 2

- D. 3

- E. 4

#### **SMT**

- How many of the following about SMT are correct?

- ① SMT makes processors with deep pipelines more tolerable to mis-predicted branches

- ② SMT can improve the throughput of a single-threaded application

- ③ SMT processors can better utilize hardware during cache misses comparing with superscalar processors with the same issue width

- MT processors can have higher cache miss rates comparing with superscalar processors with the same cache sizes when executing the same set of applications.

- A. 0

- B. 1

- C. 2

- D. 3

- E. 4

#### **SMT**

- How many of the following about SMT are correct?

- ① SMT makes processors with deep pipelines more tolerable to mis-predicted branches We can execute from other threads/contexts instead of the current one hurt, b/c you are sharing resource with other threads.

- ② SMT can improve the throughput of a single-threaded application

- ③ SMT processors can better utilize hardware during cache misses comparing with superscalar processors with the same issue width We can execute from other threads/ contexts instead of the current one

- MT processors can have higher cache miss rates comparing with superscalar processors with the same cache sizes when executing the same set of applications.

- A. 0

b/c we're sharing the cache

- B. 1

- C. 2

- D. 3

- E. 4

#### Announcement

- Project due next Monday

- Reading quiz due this Wednesday

- Assignment #5 will be up tomorrow start EARLY!!!

- iEVAL, starting tomorrow until 12/11

- Please fill the survey to let us know your opinion!

- Don't forget to take a screenshot of your submission and submit through iLearn it counts as a full credit assignment

- We will drop your lowest 2 assignment grades

- Final Exam

- Starting from 12/10 to 12/15 11:59pm (we won't provide any technical support after 12pm 12/15), any consecutive 180 minutes you pick

- Similar to the midterm, but more time and about 1.5x longer

- Will release a sample final at the end of the last lecture

- Office Hours on Zoom (the office hour link, not the lecture one)

- Hung-Wei/Prof. Usagi: M 8p-9p, W 2p-3p

- Quan Fan: F 1p-3p

# Computer Science & Engineering

203