## **Final Review**

Hung-Wei Tseng

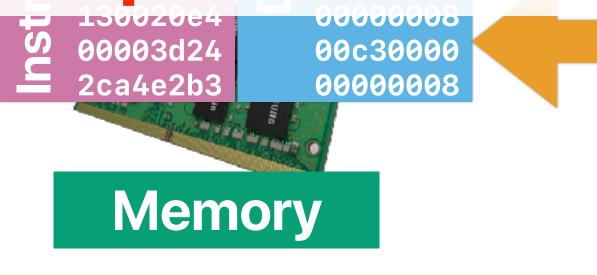

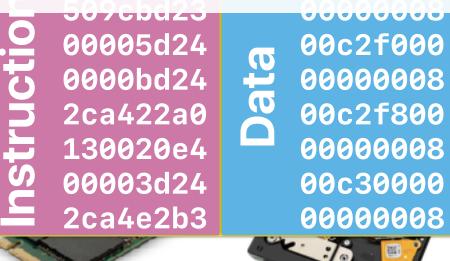

#### von Neumman Architecture

# By loading different programs into memory, your computer can perform different functions

Storage

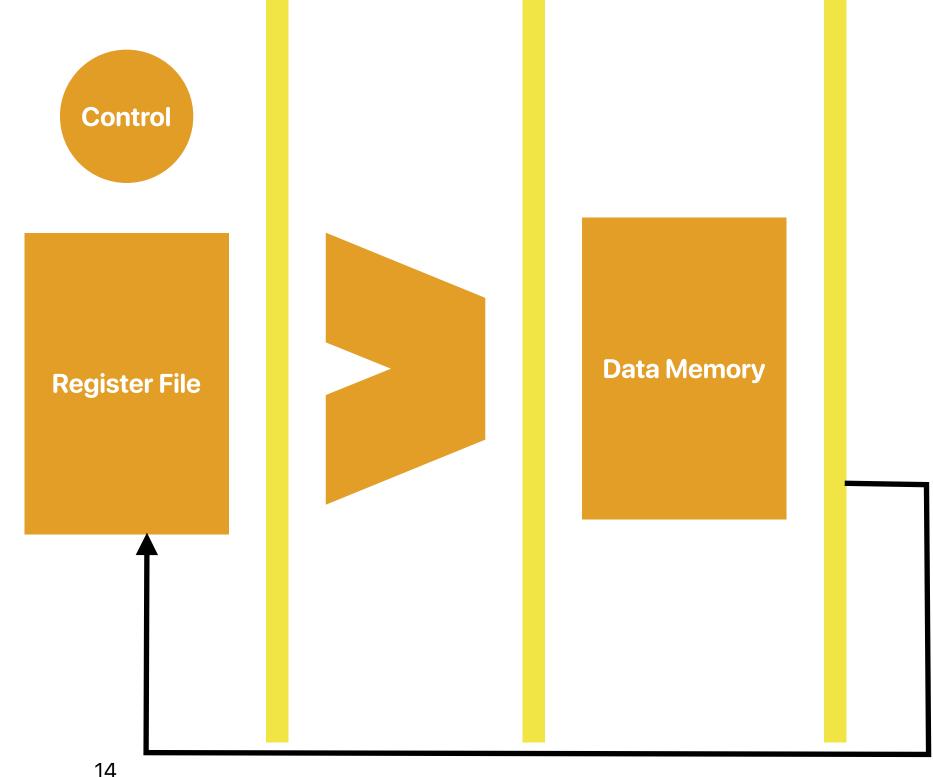

#### Tasks in processors supporting RISC-V ISA

- Instruction Fetch (IF) fetch the instruction from memory

- Instruction Decode (ID)

- Decode the instruction for the desired operation and operands

- Reading source register values

- Execution (EX)

- ALU instructions: Perform ALU operations

- Conditional Branch: Determine the branch outcome (taken/not taken)

- Memory instructions: Determine the effective address for data memory access

- Data Memory Access (MEM) Read/write memory

- Write Back (WB) Present ALU result/read value in the target register

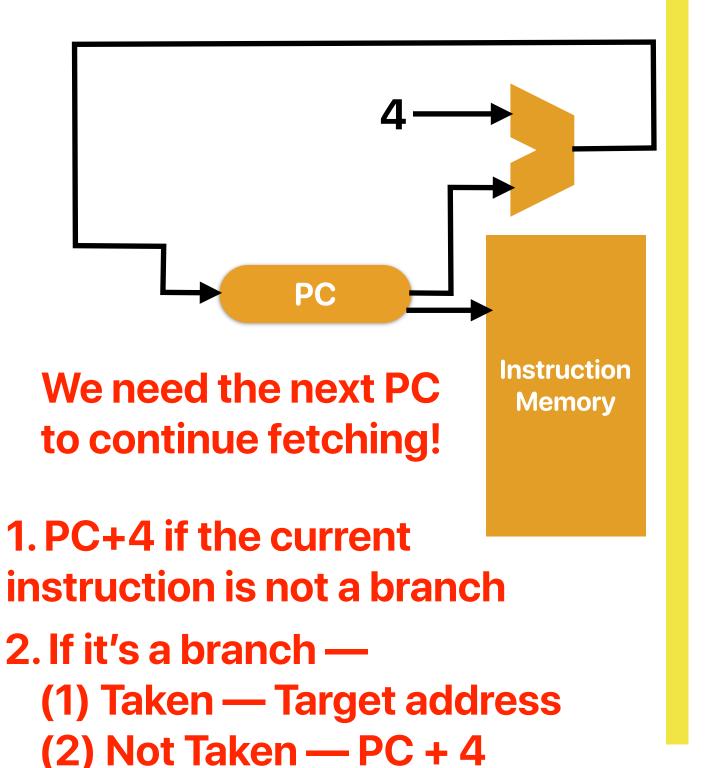

- Update PC

- If the branch is taken set to the branch target address

- Otherwise advance to the next instruction current PC + 4

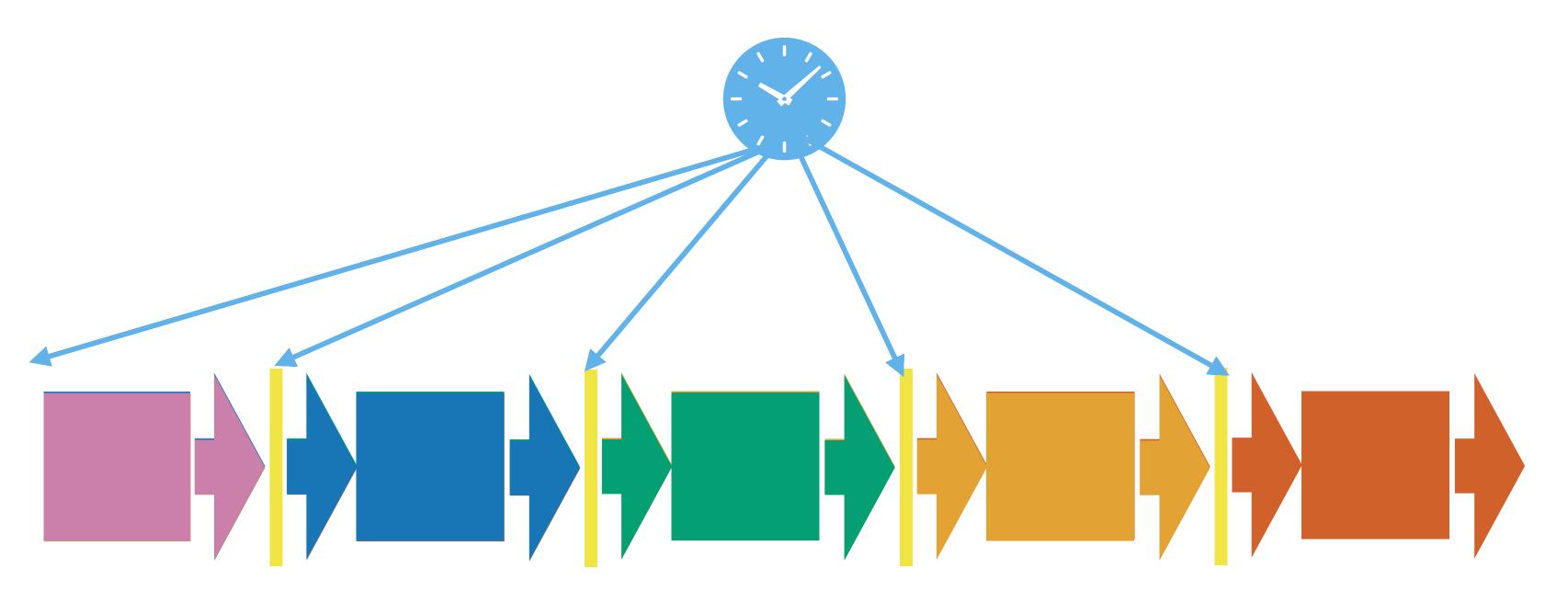

## **Pipelining**

## **Pipelining**

add x1, x2, x3 MEM WB ID EX 1d x4, 0(x5)IF ID EX MEM WB sub x6, x7, x8 MEM IF ID EX WB sub x9, x10, x11 IF EX MEM ID x1, 0(x12)ID EX IF. xor x13, x14, x15 and x16, x17, x18 add x19, x20, x21 x22, x23, x24 **1**d x25, 4(x26)sd x27, 0(x28)

Cycles

Instruction

WB

MEM WB

EX MEM WB

ID EX MEM WB

IF ID EX MEM WB

#### Three pipeline hazards

- Structural hazards resource conflicts cannot support simultaneous execution of instructions in the pipeline

- Control hazards the PC can be changed by an instruction in the pipeline

- Data hazards an instruction depending on a the result that's not yet generated or propagated when the instruction needs that

## Structural Hazards

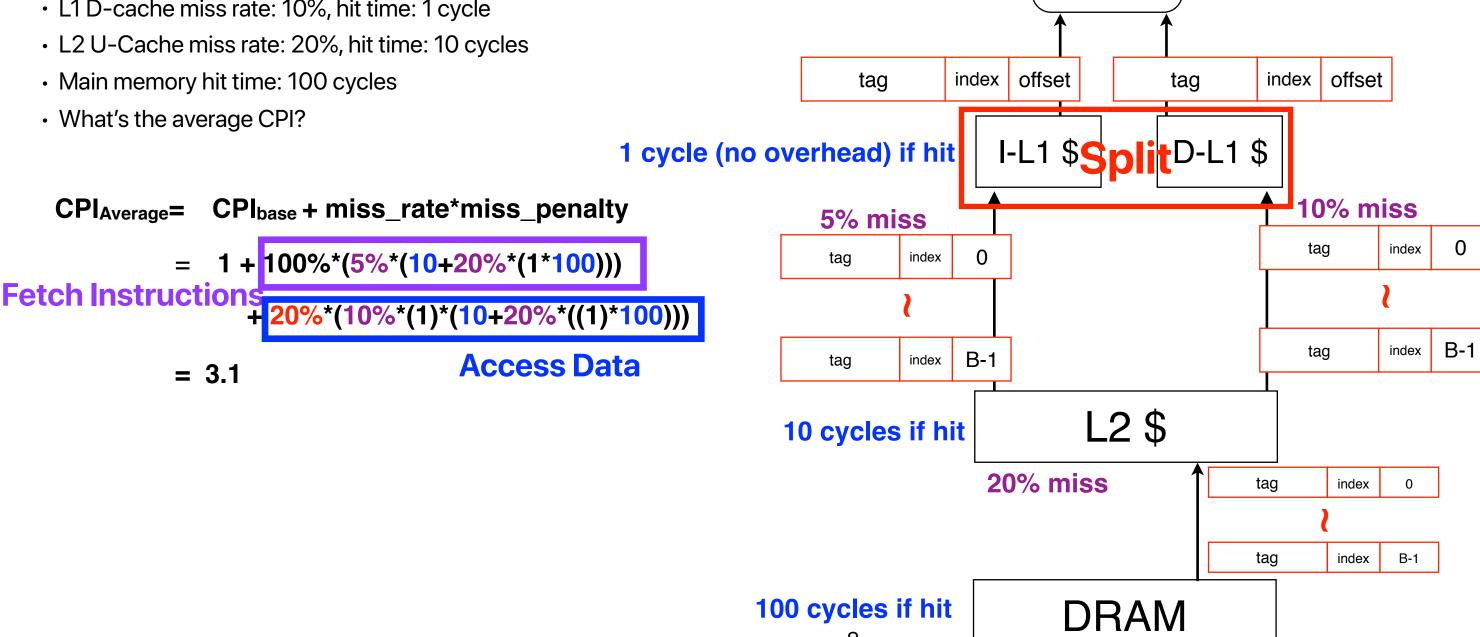

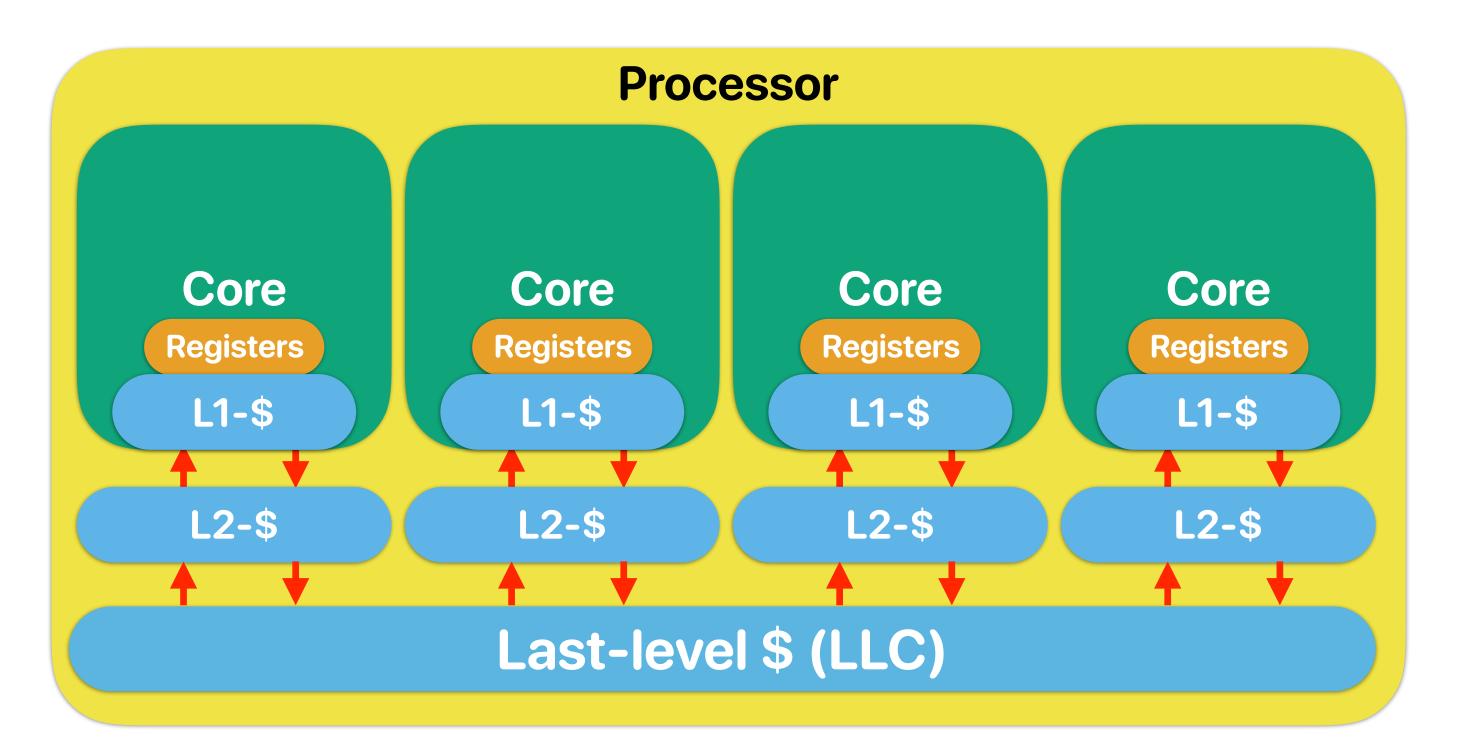

#### **Cache & Performance**

**CPU**

- Application: 80% ALU, 20% Loads

- Assume the 1-cycle L1 hit time allows the CPI to be 1

- L1 I-cache miss rate: 5%, hit time: 1 cycle

- L1 D-cache miss rate: 10%, hit time: 1 cycle

#### Dealing with the conflicts between ID/WB

- The same register cannot be read/written at the same cycle

- Better solution: write early, read late

- Writes occur at the clock edge and complete long enough before the end of the clock cycle.

- This leaves enough time for outputs to settle for reads

- The revised register file is the default one from now!

#### **Structural Hazards**

What pair of instructions will be problematic if we allow ALU instructions to skip the "MEM" stage?

```

a: 1d \times 1, 0(\times 2)

EX MEM

b: add x3, x4, x5

IF.

EX

c: sub x6, x7, x8

IF

EX

d: sub x9, x10, x11

IF

e: sd x1, 0(x12)

A. a&b

B. a & c

C. b&e

D. c&e

```

E. None

#### What if we need to support more complex or longer instructions?

If we need to support "floating point" arithmetics and it takes 4 stages for floating-point ALU execution

```

f.mul f1, f2, f3

ID

M4

M1

1d x4, 0(x5)

IF

ID

AQ

AR

MEM

WB

sub x6, x7, x8

INT

X

X

X

IF

ID

WB

```

All instructions have to be the same length in pipeline to avoid structural hazards

#### Solutions/work-around of pipeline hazards

- Structural

- Stall

- More read/write ports

- Split hardware units (e.g., instruction/data caches)

## **Control Hazards**

## A basic dynamic branch predictor

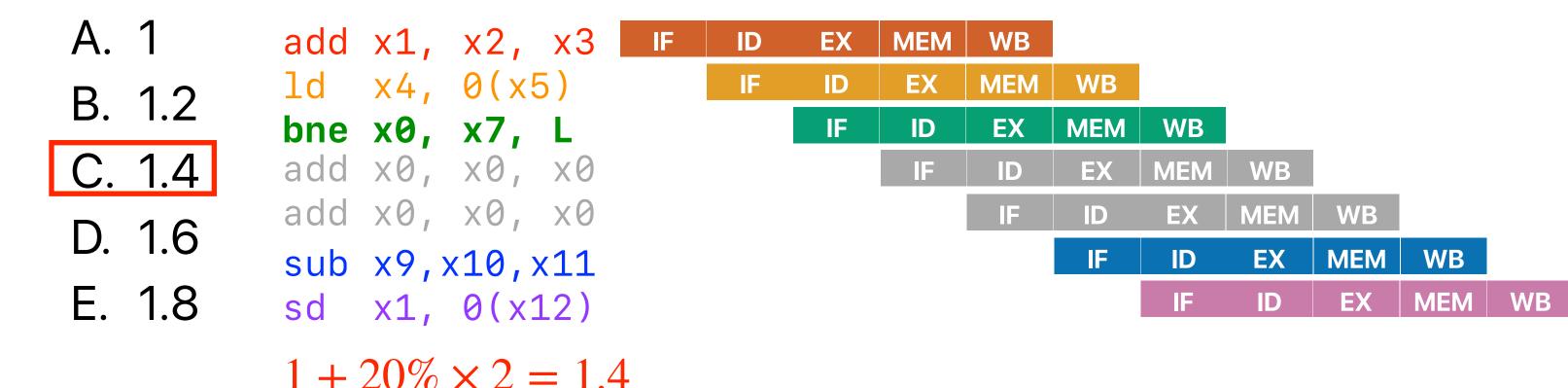

#### Let's stall whenever it's a branch

Assuming that we have an application with 20% of branch instructions and the instruction stream incurs no data hazards.

When there is a branch, we disable the instruction fetch and insert no-ops until we can determine the PC. What's the average CPI if we execute this program on the 5-stage RISC-V pipeline?

#### The frequency of branch

| Program    | Loads | Stores | Branches | Jumps | ALU operations |

|------------|-------|--------|----------|-------|----------------|

| astar      | 28%   | 6%     | 18%      | 2%    | 46%            |

| bzip       | 20%   | 7%     | 11%      | 1%    | 54%            |

| gcc        | 17%   | 23%    | 20%      | 4%    | 36%            |

| gobmk      | 21%   | 12%    | 14%      | 2%    | 50%            |

| h264ref    | 33%   | 14%    | 5%       | 2%    | 45%            |

| hmmer      | 28%   | 9%     | 17%      | 0%    | 46%            |

| libquantum | 16%   | 6%     | 29%      | 0%    | 48%            |

| mcf        | 35%   | 11%    | 24%      | 1%    | 29%            |

| omnetpp    | 23%   | 15%    | 17%      | 7%    | 31%            |

| perlbench  | 25%   | 14%    | 15%      | 7%    | 39%            |

| sjeng      | 19%   | 7%     | 15%      | 3%    | 56%            |

| xalancbmk  | 30%   | 8%     | 27%      | 3%    | 31%            |

**Figure A.29** RISC-V dynamic instruction mix for the SPECint2006 programs. Omnetpp includes 7% of the instructions that are floating point loads, stores, operations, or compares; no other program includes even 1% of other instruction types. A change in gcc in SPECint2006, creates an anomaly in behavior. Typical integer programs have load frequencies that are 1/5 to 3x the store frequency. In gcc, the store frequency is actually higher than the load frequency! This arises because a large fraction of the execution time is spent in a loop that clears memory by storing x0 (not where a compiler like gcc would usually spend most of its execution time!). A store instruction that stores a register pair, which some other RISC ISAs have included, would address this issue.

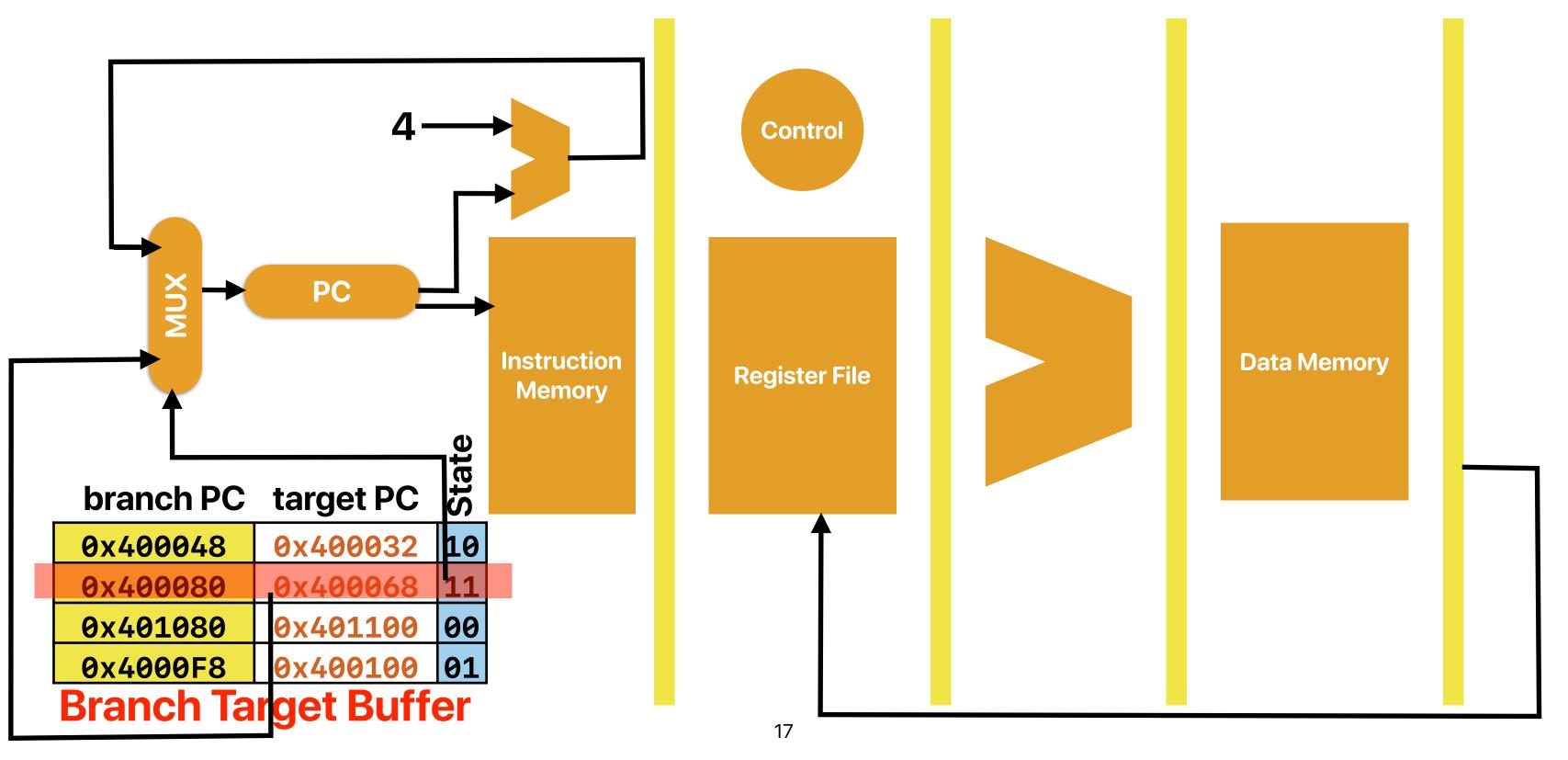

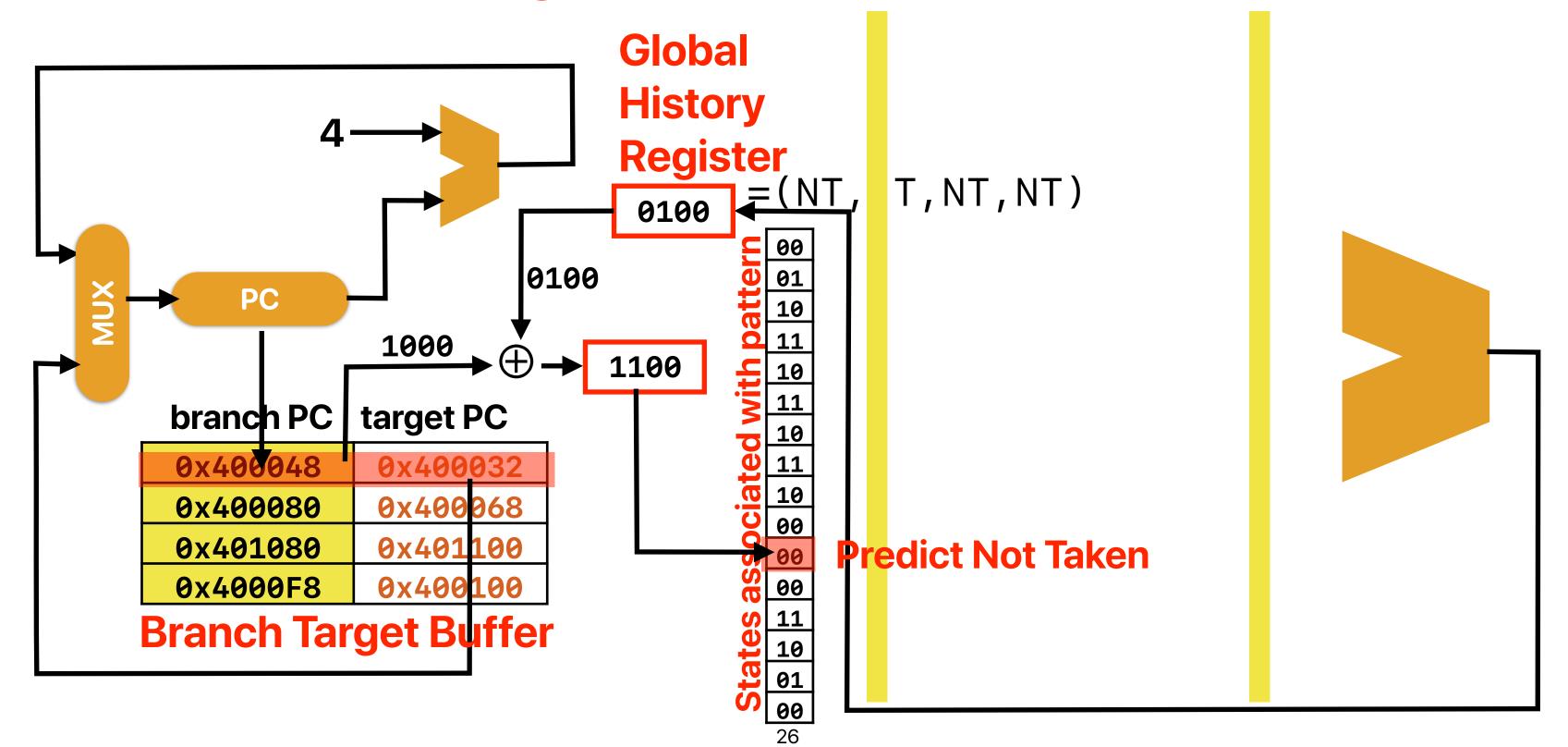

## A basic dynamic branch predictor

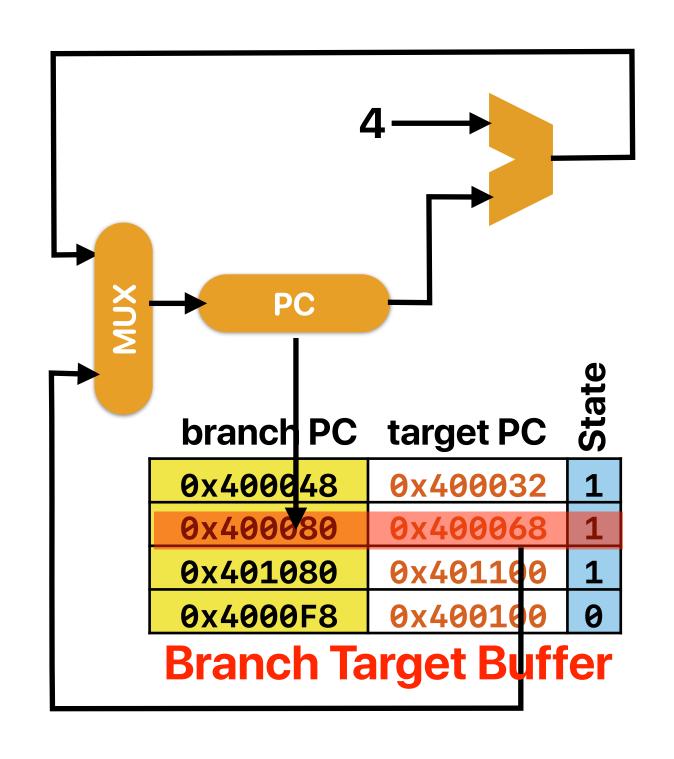

#### 2-bit/Bimodal local predictor

- Local predictor every branch instruction has its own state

- 2-bit each state is described using 2 bits

- Change the state based on actual outcome

- If we guess right no penalty

branch PC

If we guess wrong — flush (clear pipeline registers) for mis-predicted instructions that are currently in IF and ID stages and reset the PC

**Predict Taken**

0x400048

0x400032

10

0x400080

0x400068

11

0x401080

0x401100

00

0x4000F8

0x400100

01

target PC

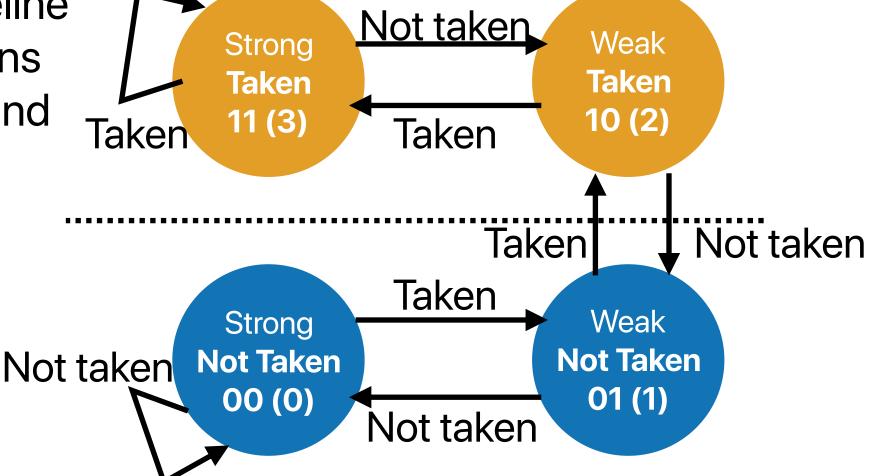

#### 2-bit local predictor

#### 2-bit local predictor

What's the overall branch prediction (include both branches) accuracy for this nested for loop?

```

i = 0;

do {

if( i % 2 != 0) // Branch X, taken if i % 2 == 0

a[i] *= 2;

a[i] += i;

} while ( ++i < 100)// Branch Y</pre>

```

(assume all states started with 00)

```

A. ~25%

```

B. ~33%

C. ~50%

D. ~67%

E. ~75%

For branch Y, almost 100%, For branch X, only 50%

| i | branch? | state | prediction | actual |

|---|---------|-------|------------|--------|

| 0 | X       | 00    | NT         | Т      |

| 1 | Υ       | 00    | NT         | Т      |

| 1 | X       | 01    | NT         | NT     |

| 2 | Υ       | 01    | NT         | Т      |

| 2 | X       | 00    | NT         | Т      |

| 3 | Υ       | 10    | Т          | Т      |

| 3 | X       | 01    | NT         | NT     |

| 4 | Υ       | 11    | Т          | Т      |

| 4 | X       | 00    | NT         | Т      |

| 5 | Y       | 11    | Т          | Т      |

| 5 | X       | 01    | NT         | NT     |

| 6 | Υ       | 11    | Т          | Т      |

| 6 | Χ       | 00    | NT         | Т      |

| 7 | Υ       | 11    | Т          | Т      |

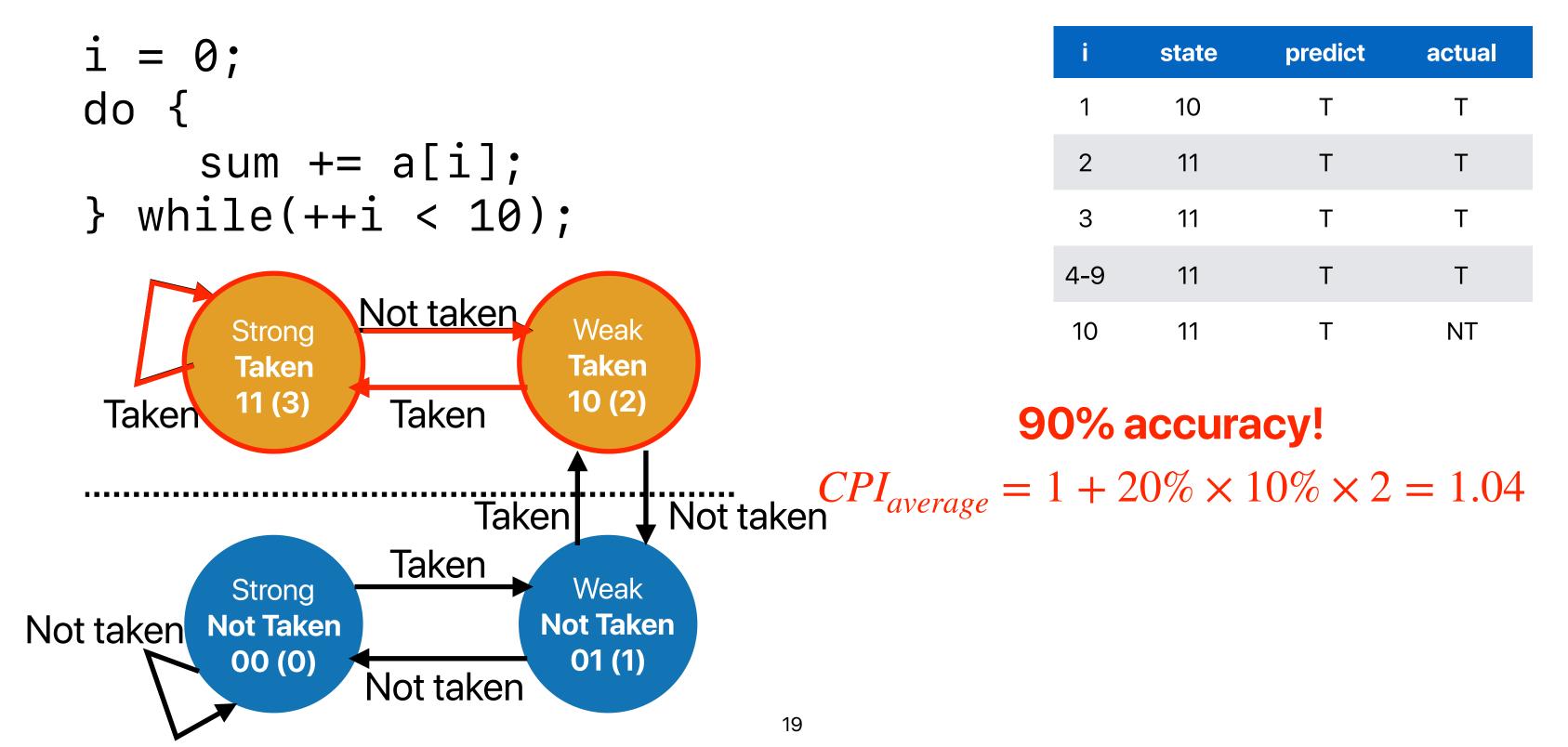

# Two-level global predictor

Reading: Scott McFarling. Combining Branch Predictors. Technical report WRL-TN-36, 1993.

## Global history (GH) predictor

#### Performance of GH predictor

```

i = 0;

do {

if( i % 2 != 0) // Branch X, taken if i % 2 == 0

a[i] *= 2;

a[i] += i;

} while ( ++i < 100)// Branch Y</pre>

```

Near perfect after this

| i  | branch? | GHR | state | prediction | actual |

|----|---------|-----|-------|------------|--------|

| 0  | Χ       | 000 | 00    | NT         | Т      |

| 0  | Y       | 001 | 00    | NT         | Т      |

| 1  | Χ       | 011 | 00    | NT         | NT     |

| 1  | Y       | 110 | 00    | NT         | Т      |

| 2  | Χ       | 101 | 00    | NT         | Т      |

| 2  | Y       | 011 | 00    | NT         | Т      |

| 3  | Χ       | 111 | 00    | NT         | NT     |

| 3  | Y       | 110 | 01    | NT         | Т      |

| 4  | Χ       | 101 | 01    | NT         | Т      |

| 4  | Y       | 011 | 01    | NT         | Т      |

| 5  | Χ       | 111 | 00    | NT         | NT     |

| 5  | Y       | 110 | 10    | Т          | Т      |

| 6  | Χ       | 101 | 10    | Т          | Т      |

| 6  | Y       | 011 | 10    | Т          | Т      |

| 7  | Χ       | 111 | 00    | NT         | NT     |

| 7  | Y       | 110 | 11    | Т          | Т      |

| 8  | X       | 101 | 11    | Т          | Т      |

| 8  | Y       | 011 | 11    | Т          | Т      |

| 9  | X       | 111 | 00    | NT         | NT     |

| 9  | Y       | 110 | 11    | Т          | Т      |

| 10 | Χ       | 101 | 11    | Т          | Т      |

| 10 | Y       | 011 | 11    | Т          | Т      |

#### **Better predictor?**

Consider two predictors — (L) 2-bit local predictor with unlimited BTB following code snippet would allow (G) to outperform (L)?

about the same about the same entries and (G) 4-bit global history with 2-bit predictors. How many of the

```

do {

if( i % 10 != 0)

a[i] *= 2;

a[i] += i;

while ( ++i < 100);

```

```

i = 0;

do {

a[i] += i;

} while ( ++i < 100);

```

```

do {

= 0;

do {

sum += A[i*2+j];

while (++j < 2);

while ( ++i < 100);

```

```

L<sub>could</sub> be bette

do {

if(rand()\%2 == 0)

a[i] *= 2;

a[i] += i;

\} while ( ++i < 100)

```

- A. 0

- C. 2

- D. 3

- E. 4

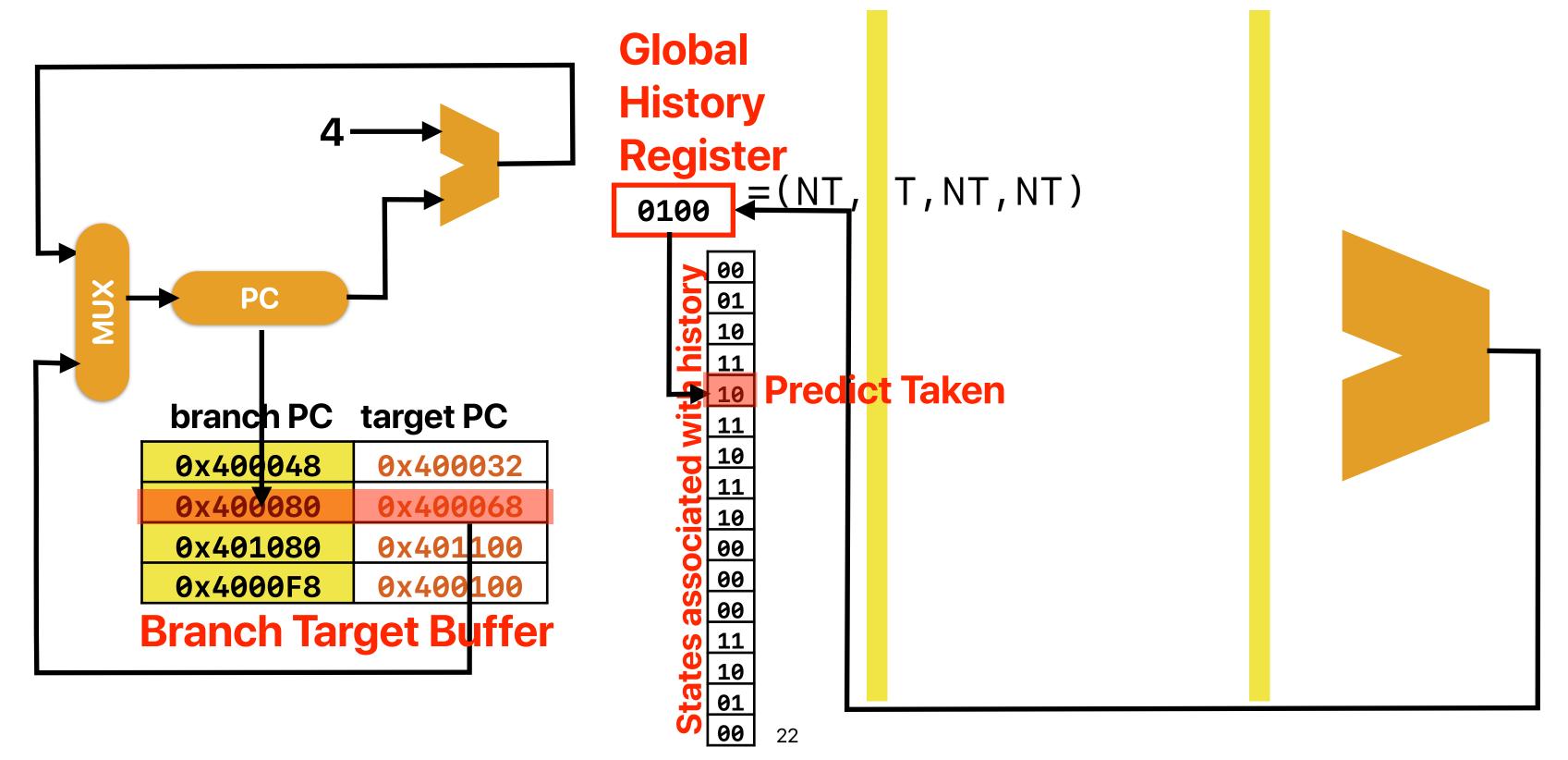

# Hybrid predictors

## gshare predictor

#### gshare predictor

Allowing the predictor to identify both branch address but also use global history for more accurate prediction

#### **Tournament Predictor**

Local

History

Predictor

branch PC local history

| 0x400048 | 1000 |

|----------|------|

| 0x400080 | 0110 |

| 0x401080 | 1010 |

| 0x4000F8 | 0110 |

#### **Tournament Predictor**

- The state predicts "which predictor is better"

- Local history

- Global history

- The predicted predictor makes the prediction

#### Branch predictor in processors

- The Intel Pentium MMX, Pentium II, and Pentium III have local branch predictors with a local 4-bit history and a local pattern history table with 16 entries for each conditional jump.

- Global branch prediction is used in Intel Pentium M, Core, Core

2, and Silvermont-based Atom processors.

- Tournament predictor is used in DEC Alpha, AMD Athlon processors

- The AMD Ryzen multi-core processor's Infinity Fabric and the Samsung Exynos processor include a perceptron based neural branch predictor.

# Branch and programming

#### **Demo revisited**

Why the sorting the array speed up the code despite the increased instruction count?

#### **Demo revisited**

- Why the performance is better when option is not "0"

- 1 The amount of dynamic instructions needs to execute is a lot smaller

- ② The amount of branch instructions to execute is smaller

- The amount of branch mis-predictions is smaller

- The amount of data accesses is smaller

|                                               | Without sorting | With sorting |

|-----------------------------------------------|-----------------|--------------|

| The prediction accuracy of X before threshold | 50%             | 100%         |

| The prediction accuracy of X after threshold  | 50%             | 100%         |

#### Four implementations

Which of the following implementations will perform the best on modern pipeline

processors?

```

inline int popcount(uint64_t x){

int c=0;

while(x) {

c += x & 1;

x = x >> 1;

}

return c;

}

```

```

inline int popcount(uint64_t x) {

int c = 0;

int table[16] = {0, 1, 1, 2, 1,

2, 2, 3, 1, 2, 2, 3, 2, 3, 3, 4};

while(x) {

c += table[(x & 0xF)];

x = x >> 4;

}

return c;

}

```

```

inline int popcount(uint64_t x) {

int c = 0;

int table[16] = {0, 1, 1, 2, 1,

2, 2, 3, 1, 2, 2, 3, 2, 3, 3, 4};

for (uint64_t i = 0; i < 16; i++)

{

c += table[(x & 0xF)];

x = x >> 4;

}

return c;

}

```

return c;

#### Why is C better than B?

How many of the following statements explains the reason why B outperforms C with compiler optimizations

C has lower dynamic instruction count than B conly needs one load, one shift, the same amount of iterations

② C has significantly lower branch mis-prediction rate than B

The same number being predicted.

3 C has significantly fewer branch instructions than B — the same amount of branches

4 C can incur fewer data hazards

— Probably not. In fact, the load may have negative

effect without architectural supports

A. 0

D. 3

```

inline int popcount(uint64_t x) {

int c = 0;

int table[16] = \{0, 1, 1, 2, 1,

2, 2, 3, 1, 2, 2, 3, 2, 3, 3, 4};

while(x)

0

c += table[(x & 0xF)];

x = x \gg 4;

return c;

```

```

inline int popcount(uint64_t x) {

int c = 0;

while(x)

c += x \& 1;

x = x >> 1;

c += x & 1;

x = x >> 1;

c += x \& 1;

x = x \gg 1;

c += x & 1;

x = x \gg 1;

return c;

```

## Why is D better than C?

How many of the following statements explains the main reason why B outperforms C with compiler optimizations

D has lower dynamic instruction count than C

— Compiler can do loop unrolling — no branches

D has significantly lower branch mis-prediction rate than C

D has significantly fewer branch instructions than C

D can incur fewer data hazards than C

A. 0

B. 1

C. 2

```

inline int popcount(uint64_t x) {

int c = 0;

int table[16] = \{0, 1, 1, 2, 1,

2, 2, 3, 1, 2, 2, 3, 2, 3, 3, 4};

while(x)

c += table[(x & 0xF)];

x = x \gg 4;

return c;

```

- maybe eliminated through loop unrolling...

```

inline int popcount(uint64_t x) {

int c = 0;

int table[16] = \{0, 1, 1, 2, 1,

2, 2, 3, 1, 2, 2, 3, 2, 3, 3, 4};

for (uint64_t i = 0; i < 16; i++)

c += table[(x & 0xF)];

x = x \gg 4;

return c;

```

### All branches are gone with loop unrolling

```

inline int popcount(uint64_t x) {

int c = 0;

int table[16] = \{0, 1, 1, 2, 1, 2, 2, 3, 1, 2, 2, 3, 2, 3, 3, 4\};

c += table[(x & 0xF)];

x = x \gg 4;

c += table[(x \& 0xF)];

x = x >> 4;

c += table[(x \& 0xF)];

x = x \gg 4;

c += table[(x & 0xF)];

x = x \gg 4;

c += table[(x \& 0xF)];

x = x >> 4;

c += table[(x \& 0xF)];

x = x \gg 4;

c += table[(x \& 0xF)];

x = x \gg 4;

c += table[(x \& 0xF)];

x = x >> 4;

c += table[(x \& 0xF)];

x = x \gg 4;

c += table[(x \& 0xF)];

x = x \gg 4;

c += table[(x \& 0xF)];

Without knowin

n the for-loop,

c += table[(x & 0xF)];

x = x >> 47

c += table[(x \& 0xF)];

x = x \gg 4;

c += table[(x \& 0xF)];

```

37

$x = x \gg 4$ ;

return c;

### Hardware acceleration

- Because popcount is important, both intel and AMD added a POPCNT instruction in their processors with SSE4.2 and SSE4a

- In C/C++, you may use the intrinsic "\_mm\_popcnt\_u64" to get # of "1"s in an unsigned 64-bit number

- You need to compile the program with -m64 -msse4.2 flags to enable these new features

```

#include <smmintrin.h>

inline int popcount(uint64_t x) {

int c = _mm_popcnt_u64(x);

return c;

}

```

### Solutions/work-around of pipeline hazards

- Structural

- Stall

- More read/write ports

- Split hardware units (e.g., instruction/data caches)

- Control

- Stalls

- Branch predictions

- Compiler optimizations with ISA supports (e.g., delayed branch)

# Data Hazards

#### **Data hazards**

- An instruction currently in the pipeline cannot receive the "logically" correct value for execution

- Data dependencies

- The output of an instruction is the input of a later instruction

- May result in data hazard if the later instruction that consumes the result is still in the pipeline

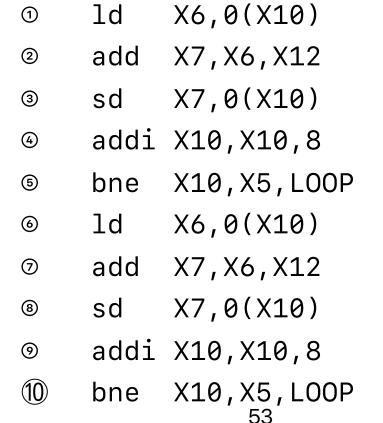

### **Example: vector scaling**

```

shl X5,X11, 3

add X5, X5, X10

do {

vector[i] += scale;

} while ( ++i < size )

sd X7, X6, X12

sd X7, 0(X10)

addi X10,X10, 8

bne X10, X5, LOOP

```

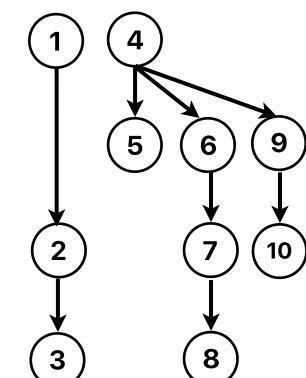

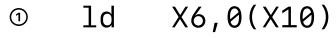

### How many dependencies do we have?

How many pairs of data dependences are there in the following RISC-V instructions?

```

ld X6, 0(X10)

add X7, X6, X12

sd X7, 0(X10)

addi X10, X10, 8

bne X10, X5, LOOP

```

```

A. 1

B. 2

C. 3

D. 4

E. 5

```

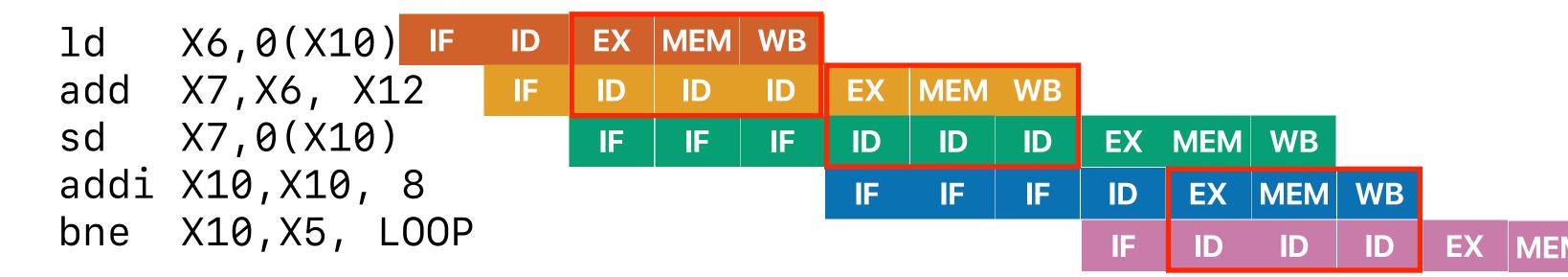

#### Stalls on data hazards

How many pairs of instructions in the following RISC-V instructions will results in data hazards/stalls in a basic 5-stage RISC-V pipeline?

- A. 1

- B. 2

- C. 3

- D. 4

- E. 5

## Solution 2: Data forwarding

- Add logics/wires to forward the desired values to the demanding instructions

- In our five stage pipeline if the instruction entering the EXE stage consumes a result from a previous instruction that is entering MEM stage or WB stage

- A source of the instruction entering EXE stage is the destination of an instruction entering MEM/WB stage

- The previous instruction must be an instruction that updates register file

### Do we still have to stall?

How many pairs of instructions in the following RISC-V instructions will results in data hazards/stalls in a basic 5-stage RISC-V pipeline with "full" data forwarding?

A. 0

B. 1

C. 2

D. 3

E. 4

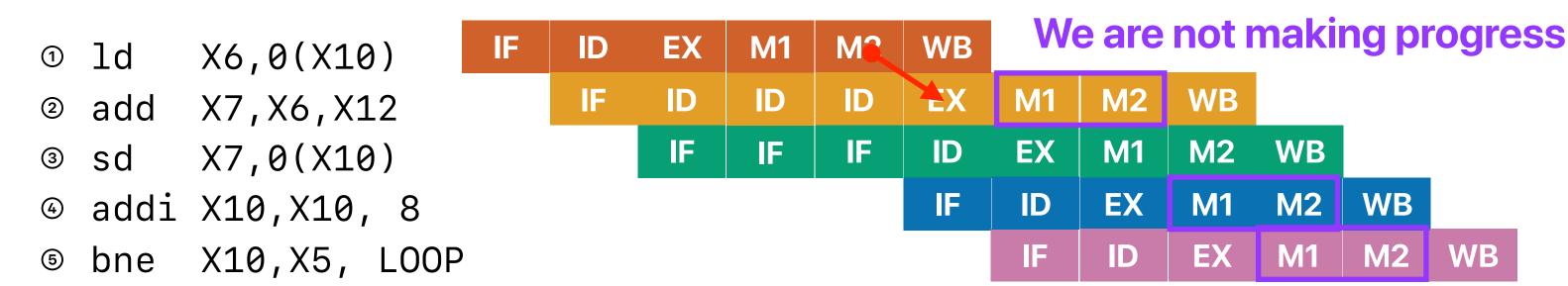

### Problems with data forwarding

• What if our pipeline gets deeper? — Considering a newly designed pipeline where memory stage is split into 2 stages and the memory access finishes at the 2nd memory stage. By reordering which pair of the following instruction stream can we eliminate all stalls without affecting the correctness of the code?

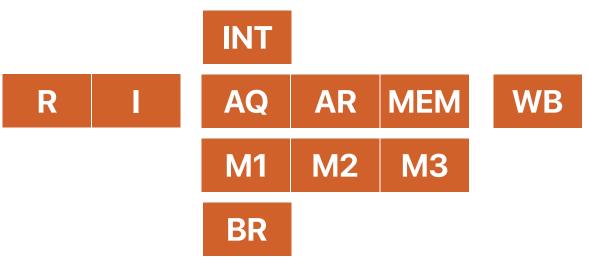

## The effect of code optimization

By reordering which pair of the following instruction stream can we eliminate all stalls without affecting the correctness of the code?

```

\bigcirc 1d X6,0(X10)

```

- 3 sd X7,0(X10)

- @ addi X10,X10, 8

- ⑤ bne X10,X5, LOOP

- A. (1) & (2)

- B. (2) & (3)

- C. (3) & (4)

- D. (4) & (5)

- E. None of the pairs can be reordered

### If we can predict the future ...

Consider the following dynamic instructions:

```

① ld X6,0(X10)

```

- addi X10,X10, 8

- 10 bne X10, X5, LOOP

Can we use "branch prediction" to predict the future and reorder instructions across the branch?

Which of the following pair can we reorder without affecting the correctness if the branch prediction is perfect?

- A. (2) and (4)

- B. (3) and (5)

- C. (5) and (6)

- D. (6) and (9)

- E. (9) and (10)

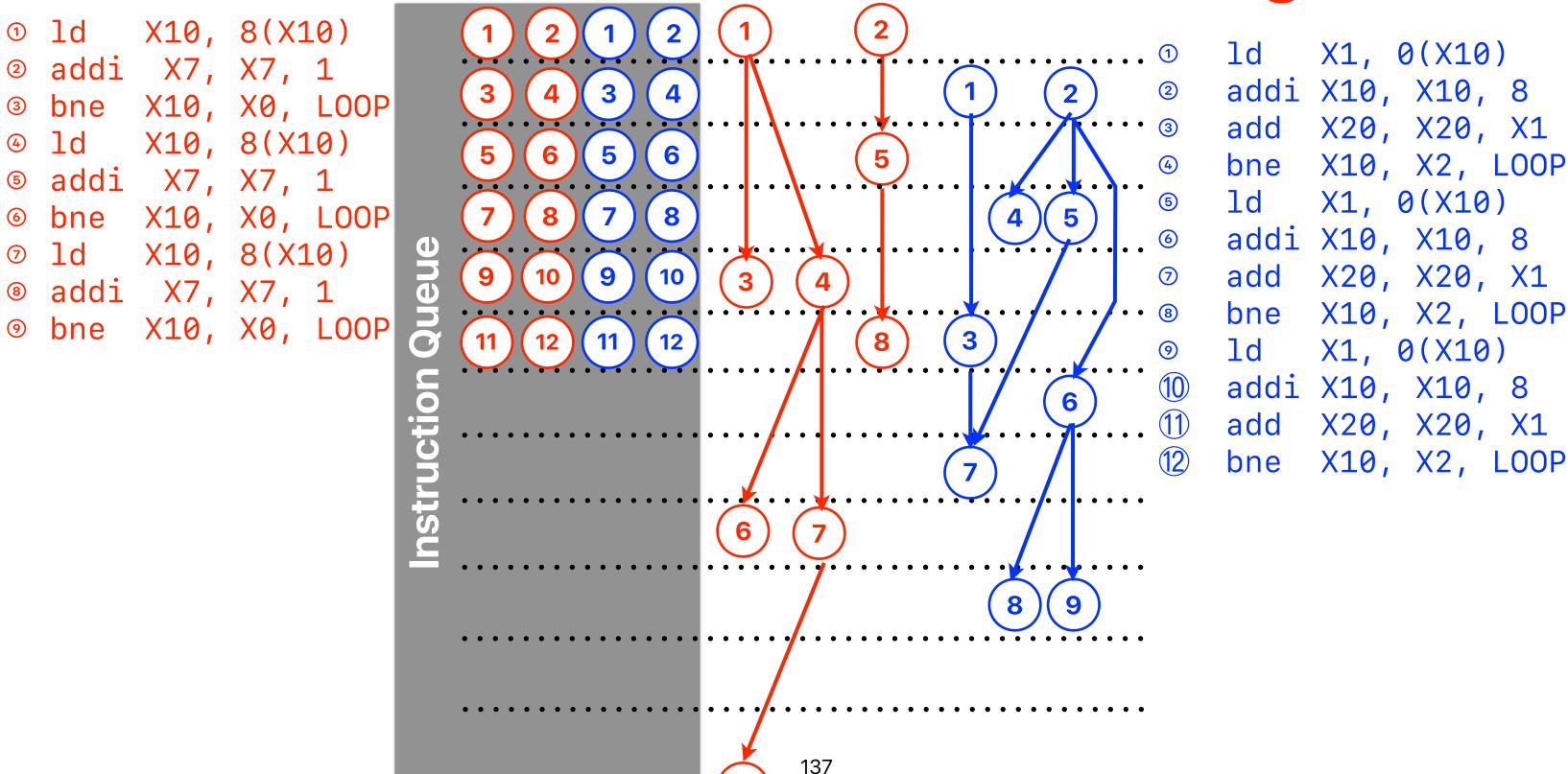

# Dynamic instruction scheduling/ Out-of-order (OoO) execution

## Tips of drawing a pipeline diagram

- Each instruction has to go through all 5 pipeline stages: IF, ID, EXE, MEM,

WB in order only valid if it's single-issue, RISC-V 5-stage pipeline

- · An instruction can enter the next pipeline stage in the next cycle if

- No other instruction is occupying the next stage

- · This instruction has completed its own work in the current stage

- The next stage has all its inputs ready

- Fetch a new instruction only if

- We know the next PC to fetch

- We can predict the next PC

- Flush an instruction if the branch resolution says it's mis-predicted.

### If we can predict the future ...

- Consider the following dynamic instructions:

- ① ld X6,0(X10)

- @ add X7, X6, X12

- 3 sd X7,0(X10)

- @ addi X10,X10, 8

- © bne X10,X5, LOOP

- © ld X6,0(X10)

- ② add X7,X6, X12

- ® sd X7,0(X10)

- addi X10,X10, 8

- 10 bne X10, X5, LOOP

Which of the following pair can we reorder without affecting the correctness if the branch prediction is perfect?

- A. (2) and (4)

- B. (3) and (5)

- C. (5) and (6)

- D. (6) and (9)

- E. (9) and (10)

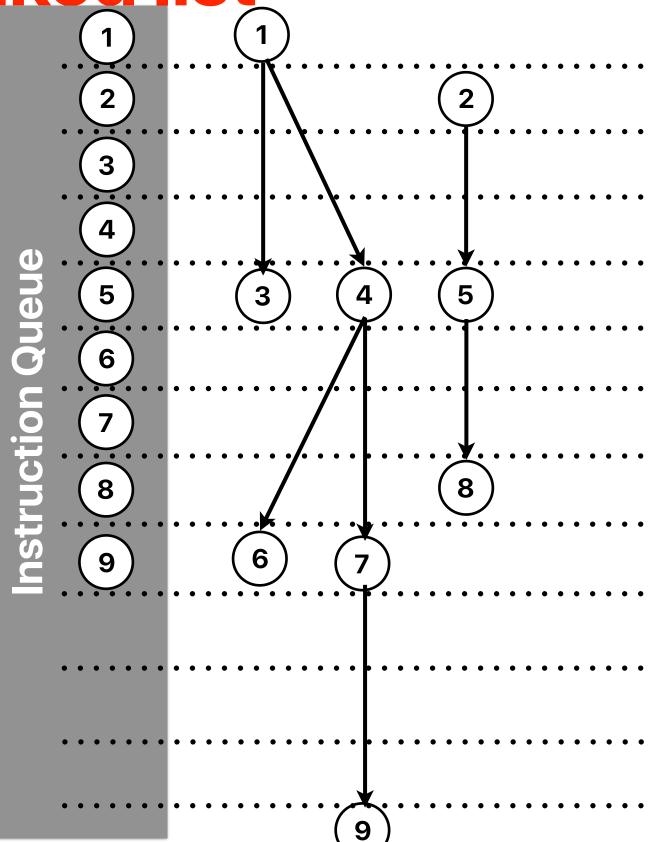

We still can only reorder (5) and (6) even though (2) & (4) are not depending on each other!

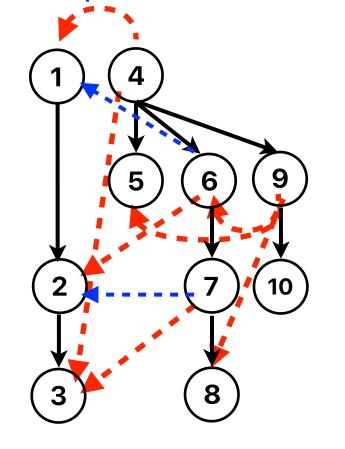

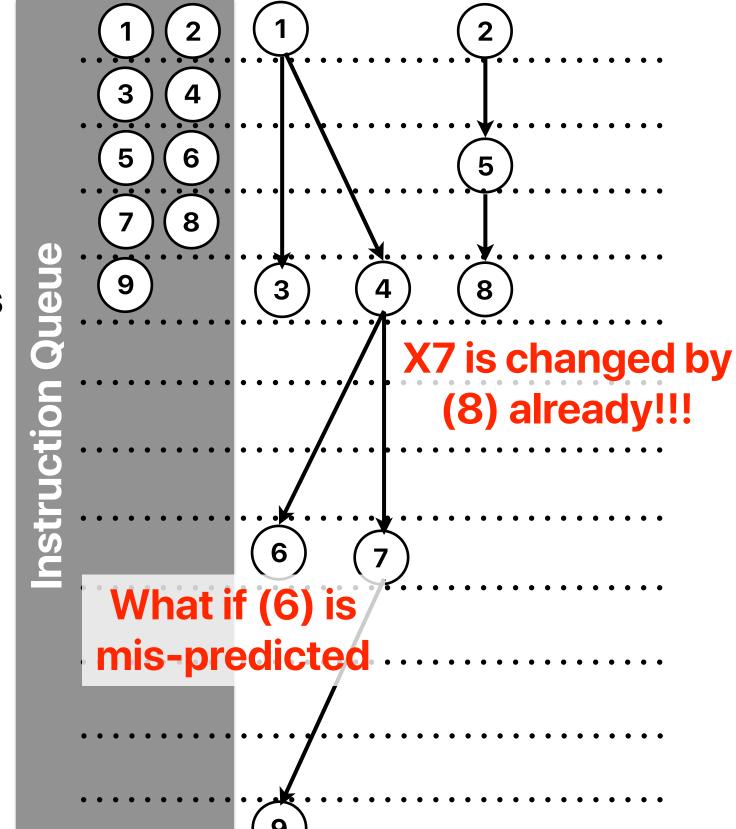

### False dependencies

- We are still limited by false dependencies because we have instructions without dependencies sharing registers!

- They are not "true" dependencies because they don't have an arrow in data dependency graph

- WAR (Write After Read): a later instruction overwrites the source of an earlier one

- 4 and 1 4 and 3, 6 and 2, 7 and 3, 9 and 5, 9 and 6, 9 and 8

- WAW (Write After Write): a later instruction overwrites the output of an earlier one

- 6 and 1, 7 and 2

## Eliminating false dependencies

- We're constrained in scheduling because instructions

- WAR a "logically" later instruction overwrites the input register

- WAW a "logically" later instruction overwrites the output register

- Since all the issues arises from "overwriting" rename the output registers for instructions

- Two different mechanisms introduced

- Tomasulo algorithm rename/remap output to reservation stations

- Register renaming rename/remap output to physical registers

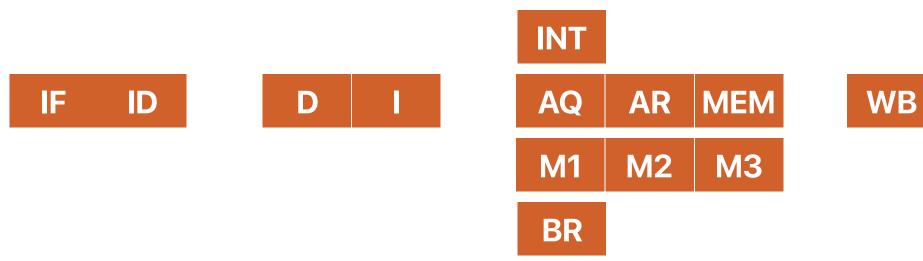

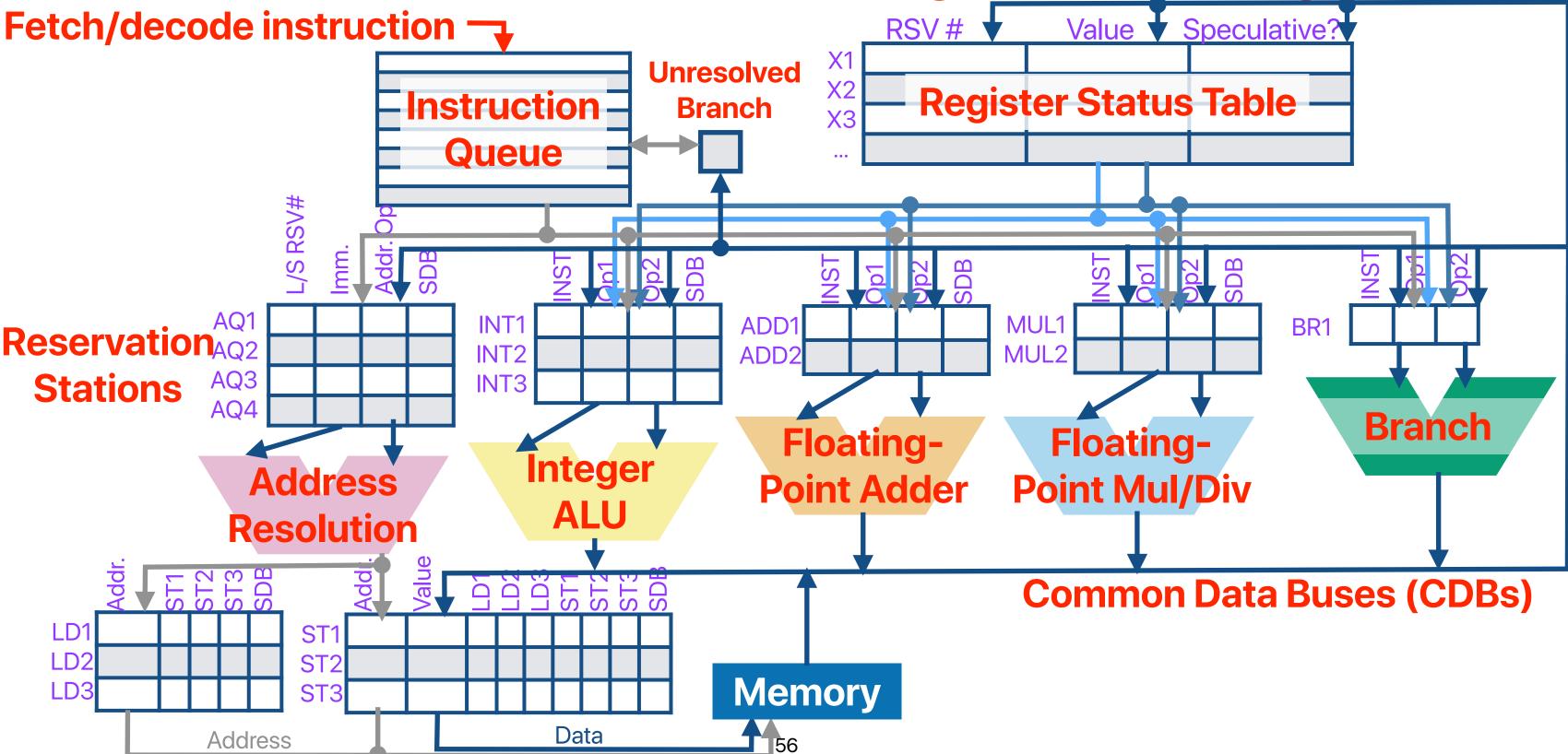

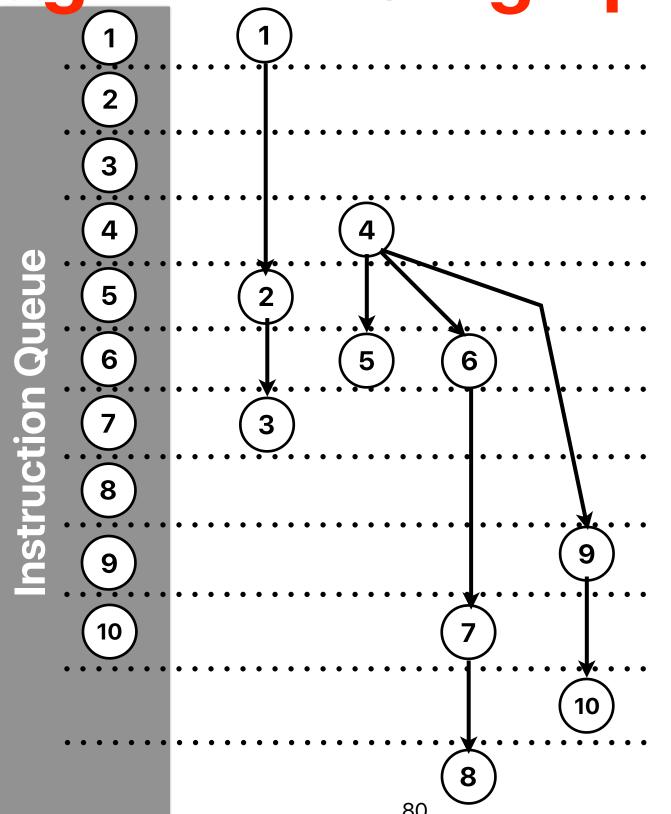

### Pipeline in Tomasulo

- Dispatch (D) allocate a "reservation station" for a decoded instruction

- Issue (I) collect pending values/branch outcome from common data bus

- Execute (INT, AQ/AQ/MEM, M1/M2/M3, BR) send the instruction to its corresponding pipeline if no structural hazards

- Write Back (WB) broadcast the result through CDB

Overview of a processor supporting Tomasulo's algorithm

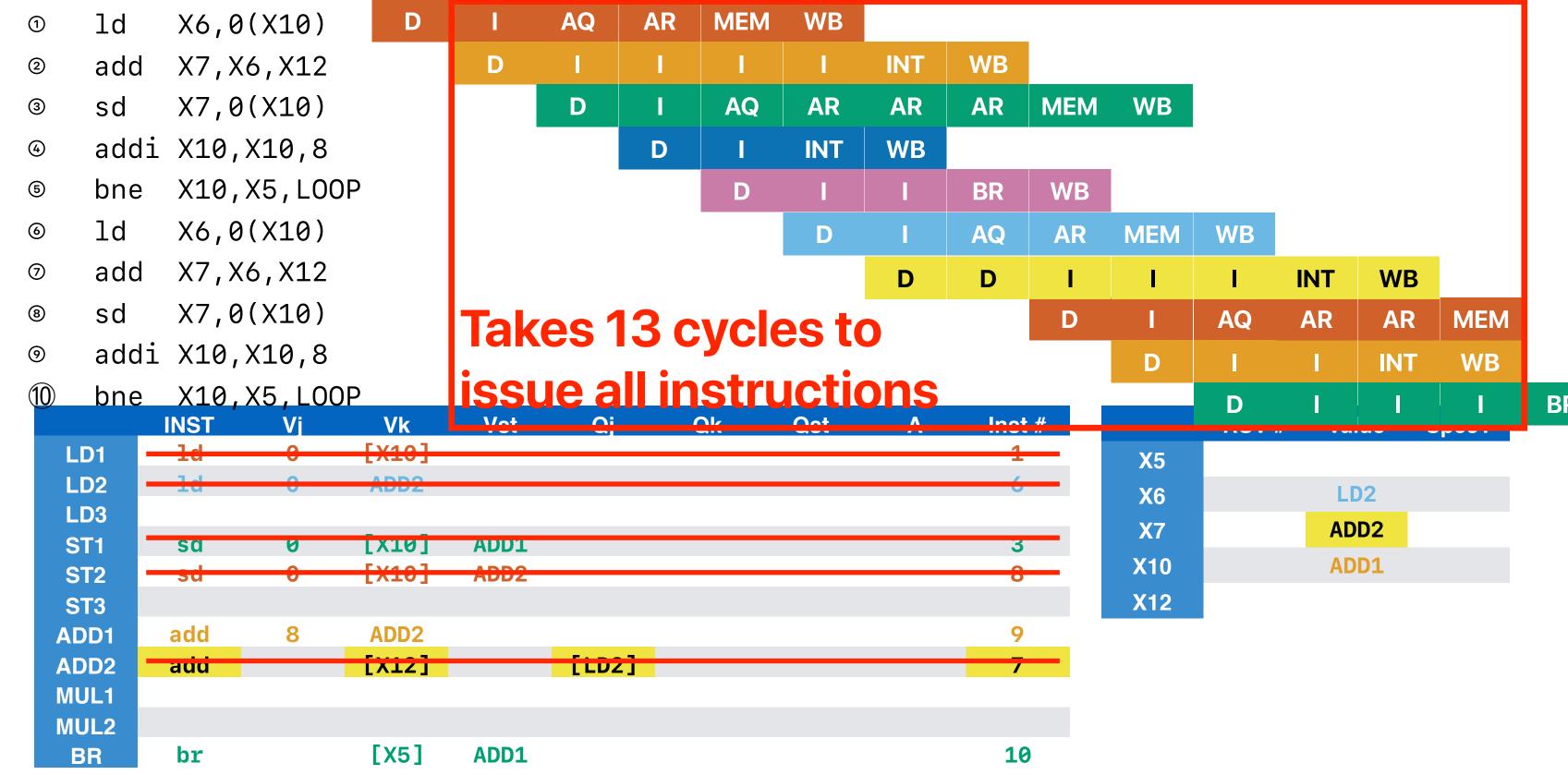

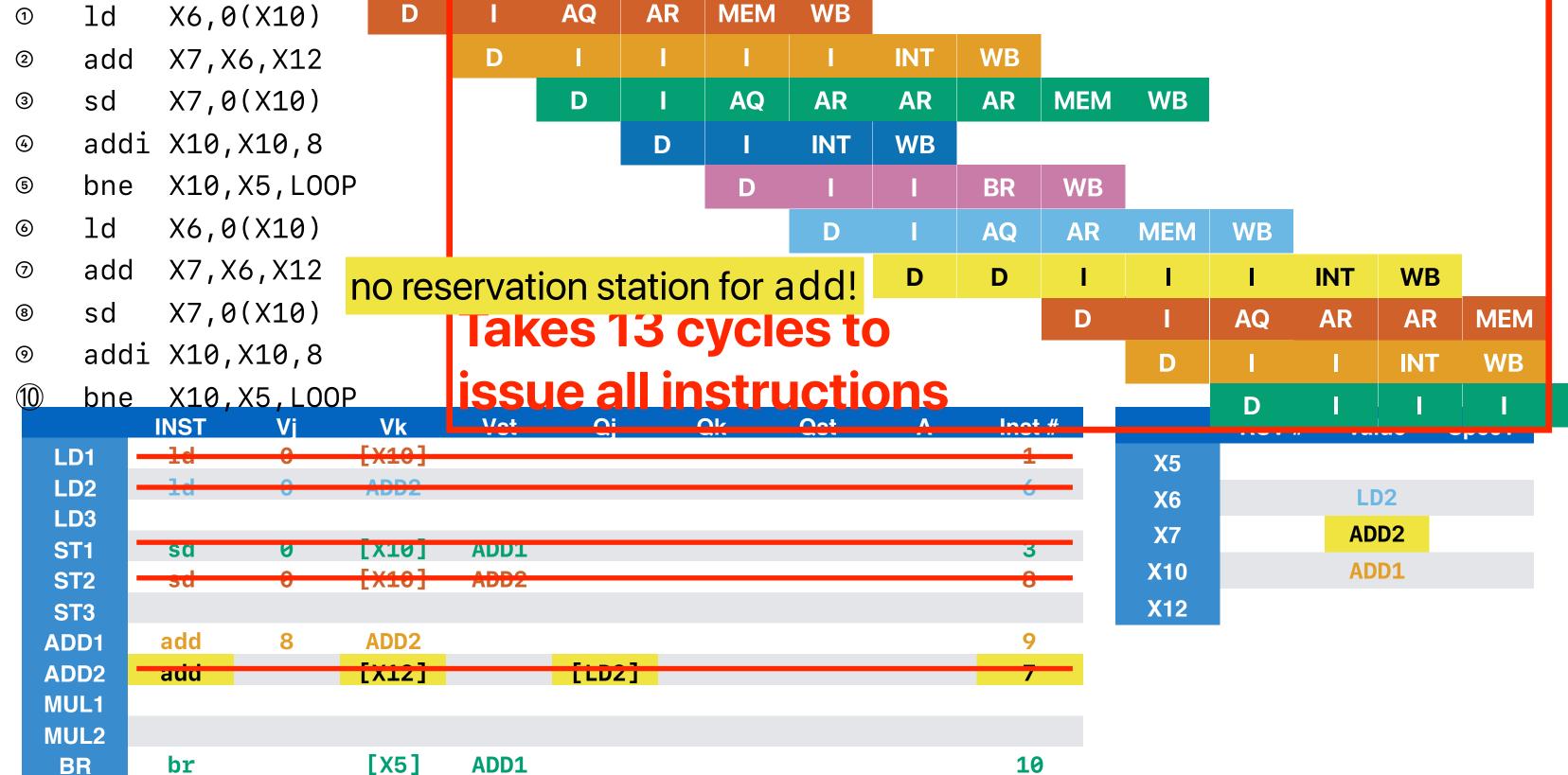

Tomasulo in motion

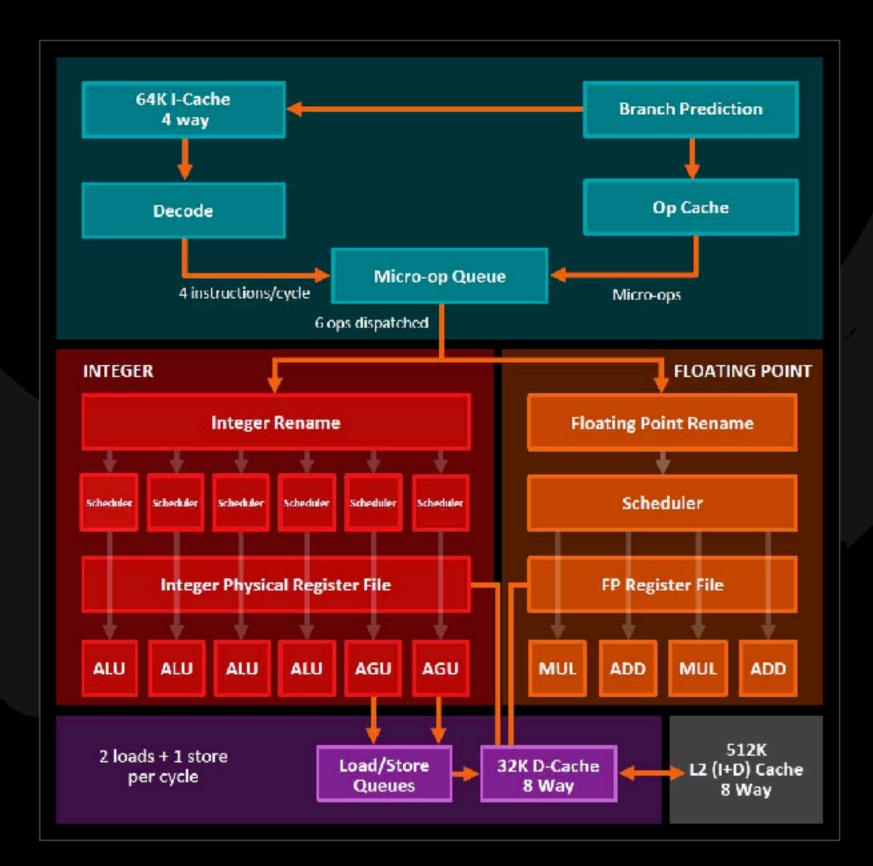

# Register renaming

- K. C. Yeager, "The Mips R10000 superscalar microprocessor," in IEEE Micro, vol. 16, no. 2, pp. 28-41, April 1996.

- R. E. Kessler, "The Alpha 21264 microprocessor," in IEEE Micro, vol. 19, no. 2, pp. 24–36,

March-April 1999.

Tomasulo in motion

B

### Recap: Why is B better than A?

```

inline int popcount(uint64_t x){

int c=0;

while(x) {

c += x & 1;

x = x >> 1;

}

return c;

}

```

```

inline int popcount(uint64_t x) {

int c = 0;

while(x) {

c += x & 1;

x = x >> 1;

c += x & 1;

x = x >> 1;

c += x & 1;

x = x >> 1;

c += x & 1;

x = x >> 1;

c += x & 1;

x = x >> 1;

c += x & 1;

x = x >> 1;

c += x & 1;

x = x >> 1;

}

return c;

}

```

```

and x2, x1, 1

add x3, x3, x2

shr x1, x1, 1

bne x1, x0, LOOP

4*n instructions

x1, 1

and

x1, 1

and

x3 x3, x2

shr

x4, x1, 1

add

x1 x1, 1

x5, x1, 2

shr

shr

x1, 1

shr

x6, x1, 3

and

x3 x3, x2

x1, 4

add

shr

x1, 1

x4, 1

shr

and

x1, 1

x8, x5, 1

and

and

x3 x3, x2

x9, x6, 1

and

add

x1, 1

x3, x3, x2

add

shr

x1, 1

x3, x3, x7

add

and

x3 x3, x2

x3, x3, x8

add

add

x1, 1

x3, x9

shr

add

x0, LOOP

x0, LOOP

bne

bne

13*(n/4) = 3.25*n instructions

```

60 Only one branch for four iterations in A

### Recap: Why is B better than A?

```

and

x^{2}, x^{1}, 1

add

shr

and

add

shr

and

add

x3, x2

x3,

shr

and

add

х3,

shr

LOOP

bne

```

```

and

shr

shr

shr

x6

shr

and

and

and

add

x3,

add

x3, x7

add

x3, x8

add

x3, x9

bne

x0, LOOP

```

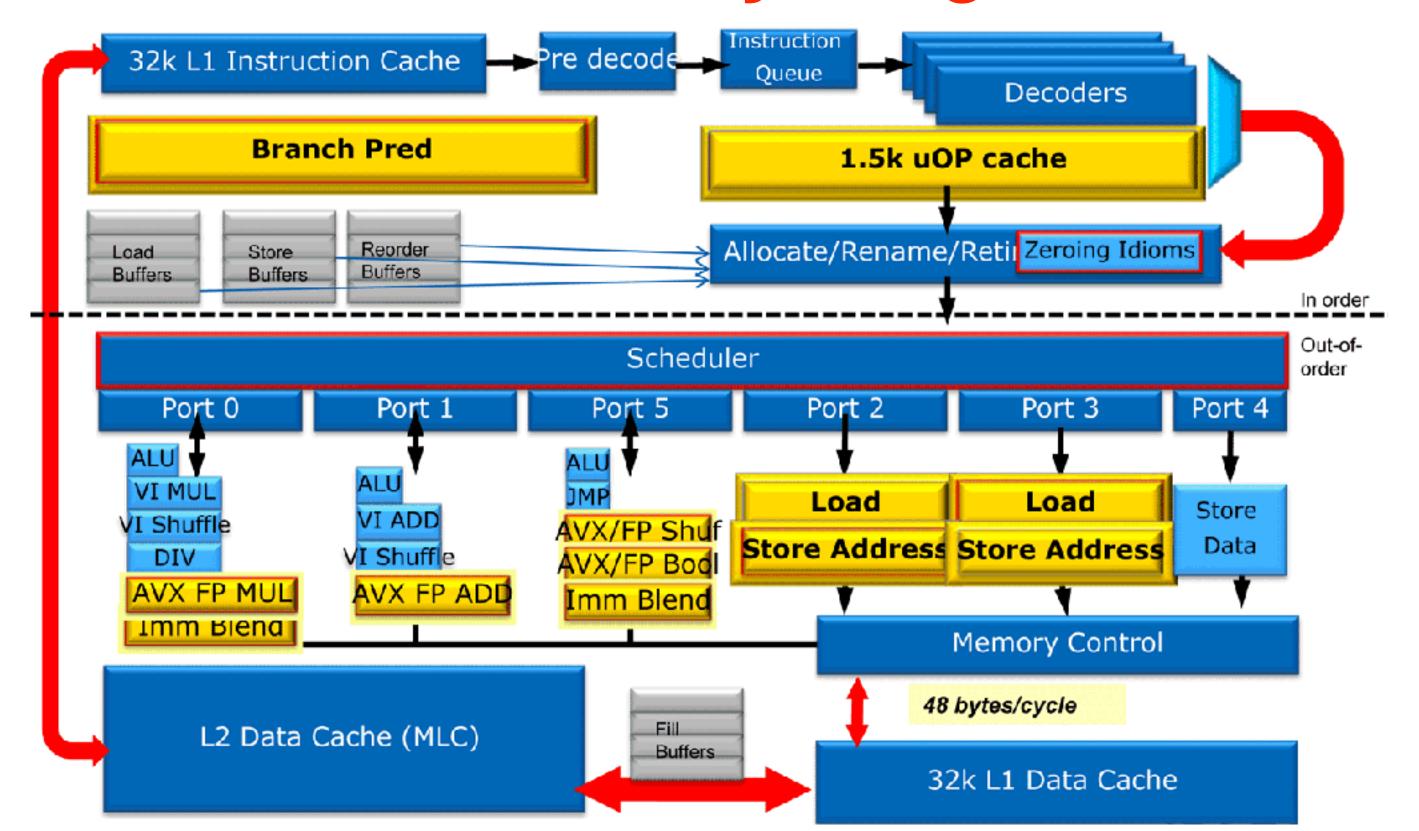

## Register renaming

- Decouple "reservation stations" from functional units

- Provide a set of "physical registers" and a mapping table mapping "architectural registers" to "physical registers"

- Allocate a physical register for a new output

- Stages

- Dispatch (D) allocate a "physical" for the output of a decoded instruction

- Issue (I) collect pending values/branch outcome from common data bus

- Execute (INT, AQ/AQ/MEM, M1/M2/M3, BR) send the instruction to its corresponding pipeline if no structural hazards

- Write Back (WB) broadcast the result through CDB

Overview of a processor supporting register renaming Fetch/decode instruction physical Renaming **Unresolved** X1 register # **Branch** logic **Physical** Register Registers mapping table Instruction -Queue Address Floating-Floating-Integer **Branch Point Adder Point Mul/Div** Resolution **ALU Store** Load Queue Queue **Memory** Data Address

```

① ld X6,0(X10)

```

- ② add X7,X6,X12

- 3 sd X7,0(X10)

- addi X10,X10,8

- bne X10, X5, L00P

- © ld X6,0(X10)

- ② add X7, X6, X12

- sd X7,0(X10)

- addi X10,X10,8

- 10 bne X10, X5, LOOP

|    | Re         | named | instruction |  |

|----|------------|-------|-------------|--|

| 1  | <b>1</b> d | P1,   | 0(X10)      |  |

| 2  |            |       |             |  |

| 3  |            |       |             |  |

| 4  |            |       |             |  |

| 5  |            |       |             |  |

| 6  |            |       |             |  |

| 7  |            |       |             |  |

| 8  |            |       |             |  |

| 9  |            |       |             |  |

| 10 |            |       |             |  |

|            | Physical Register |

|------------|-------------------|

| <b>X</b> 5 |                   |

| <b>X6</b>  | P1                |

| <b>X7</b>  |                   |

| X10        |                   |

| X12        |                   |

|           | Valid | Value | In use |            | Valid | Value | In use |

|-----------|-------|-------|--------|------------|-------|-------|--------|

| P1        | 0     |       | 1      | P6         |       |       |        |

| P2        |       |       |        | <b>P</b> 7 |       |       |        |

| <b>P3</b> |       |       |        | P8         |       |       |        |

| P4        |       |       |        | <b>P9</b>  |       |       |        |

| <b>P5</b> |       |       |        | P10        |       |       |        |

```

① ld X6,0(X10) R I

② add X7,X6,X12 R

```

- 3 sd X7,0(X10)

- addi X10,X10,8

- ⑤ bne X10,X5,L00P

- © ld X6,0(X10)

- ② add X7,X6,X12

- sd X7,0(X10)

- 9 addi X10,X10,8

- 10 bne X10, X5, LOOP

|    | Rer        | named | instr      | uction |

|----|------------|-------|------------|--------|

| 1  | <b>1</b> d | P1,   | <b>0(X</b> | 10)    |

| 2  | add        | P2,   | P1,        | X12    |

| 3  |            |       |            |        |

| 4  |            |       |            |        |

| 5  |            |       |            |        |

| 6  |            |       |            |        |

| 7  |            |       |            |        |

| 8  |            |       |            |        |

| 9  |            |       |            |        |

| 10 |            |       |            |        |

|            | Physical Register |

|------------|-------------------|

| <b>X</b> 5 |                   |

| <b>X6</b>  | P1                |

| <b>X7</b>  | P2                |

| X10        |                   |

| X12        |                   |

|            | Valid | Value | In use |           | Valid | Value | In use |

|------------|-------|-------|--------|-----------|-------|-------|--------|

| P1         | 0     |       | 1      | P6        |       |       |        |

| P2         | 0     |       | 1      | <b>P7</b> |       |       |        |

| <b>P3</b>  |       |       |        | P8        |       |       |        |

| P4         |       |       |        | P9        |       |       |        |

| <b>P</b> 5 |       |       |        | P10       |       |       |        |

```

1 ld X6,0(X10) R I AR

2 add X7,X6,X12 R I

3 sd X7,0(X10) R

```

- addi X10,X10,8

- 5 bne X10,X5,L00P

- © ld X6,0(X10)

- ② add X7, X6, X12

- sd X7,0(X10)

- 9 addi X10,X10,8

- ① bne X10, X5, LOOP

|    | Renamed instruction |     |        |    |  |  |

|----|---------------------|-----|--------|----|--|--|

| 1  | <b>1</b> d          | P1, | 0(X10) |    |  |  |

| 2  | add                 | P2, | P1, X1 | L2 |  |  |

| 3  | sd                  | P2, | 0(X10) |    |  |  |

| 4  |                     |     |        |    |  |  |

| 5  |                     |     |        |    |  |  |

| 6  |                     |     |        |    |  |  |

| 7  |                     |     |        |    |  |  |

| 8  |                     |     |        |    |  |  |

| 9  |                     |     |        |    |  |  |

| 10 |                     |     |        |    |  |  |

|            | Physical Register |

|------------|-------------------|

| <b>X</b> 5 |                   |

| <b>X6</b>  | P1                |

| <b>X7</b>  | P2                |

| X10        |                   |

| X12        |                   |

|           | Valid | Value | In use |            | Valid | Value | In use |

|-----------|-------|-------|--------|------------|-------|-------|--------|

| P1        | 0     |       | 1      | P6         |       |       |        |

| P2        | 0     |       | 1      | <b>P</b> 7 |       |       |        |

| <b>P3</b> |       |       |        | P8         |       |       |        |

| P4        |       |       |        | <b>P</b> 9 |       |       |        |

| <b>P5</b> |       |       |        | P10        |       |       |        |

| 1 | ld   | X6,0(X10) | R |   | AR | LSQ |

|---|------|-----------|---|---|----|-----|

| 2 | add  | X7,X6,X12 |   | R | I  | - 1 |

| 3 | sd   | X7,0(X10) |   |   | R  | 1   |

| 4 | addi | X10,X10,8 |   |   |    | R   |

- © bne X10,X5,L00P

- © ld X6,0(X10)

- ② add X7,X6,X12

- ® sd X7,0(X10)

- addi X10,X10,8

- ① bne X10, X5, LOOP

|    | Ren        | amed | instruction |

|----|------------|------|-------------|

| 1  | <b>1</b> d | P1,  | 0(X10)      |

| 2  | add        | P2,  | P1, X12     |

| 3  | sd         | P2,  | 0(X10)      |

| 4  | addi       | Р3,  | X10, 8      |

| 5  |            |      |             |

| 6  |            |      |             |

| 7  |            |      |             |

| 8  |            |      |             |

| 9  |            |      |             |

| 10 |            |      |             |

|           | Physical Register |

|-----------|-------------------|

| <b>X5</b> |                   |

| <b>X6</b> | P1                |

| <b>X7</b> | P2                |

| X10       | Р3                |

| X12       |                   |

|            | Valid | Value | In use |            | Valid | Value | In use |

|------------|-------|-------|--------|------------|-------|-------|--------|

| P1         | 0     |       | 1      | P6         |       |       |        |

| P2         | 0     |       | 1      | <b>P</b> 7 |       |       |        |

| <b>P</b> 3 | 0     |       | 1      | P8         |       |       |        |

| P4         |       |       |        | <b>P</b> 9 |       |       |        |

| <b>P5</b>  |       |       |        | P10        |       |       |        |

| 1 | ld  | X6,0(X10) | R | I | AR | LSQ | ME |

|---|-----|-----------|---|---|----|-----|----|

| 2 | add | X7,X6,X12 |   | R | 1  | I   | ı  |

| 3 | sd  | X7,0(X10) |   |   | R  |     |    |

|   |     |           |   |   |    |     |    |

- addi X10,X10,8

- 5 bne X10,X5,L00P

- © ld X6,0(X10)

- ② add X7,X6,X12

- 8 sd X7,0(X10)

- 9 addi X10,X10,8

- 10 bne X10, X5, LOOP

|    | Ren        | amed | instruction |  |

|----|------------|------|-------------|--|

| 1  | <b>1</b> d | P1,  | 0(X10)      |  |

| 2  | add        | P2,  | P1, X12     |  |

| 3  | sd         | P2,  | 0(X10)      |  |

| 4  | addi       | P3,  | X10, 8      |  |

| 5  | bne        | P3,  | X5, LOOP    |  |

| 6  |            |      |             |  |

| 7  |            |      |             |  |

| 8  |            |      |             |  |

| 9  |            |      |             |  |

| 10 |            |      |             |  |

|            | Physical Register |

|------------|-------------------|

| <b>X</b> 5 |                   |

| <b>X6</b>  | P1                |

| <b>X7</b>  | P2                |

| X10        | Р3                |

| X12        |                   |

|            | Valid | Value | In use |            | Valid | Value | In use |

|------------|-------|-------|--------|------------|-------|-------|--------|

| P1         | 0     |       | 1      | P6         |       |       |        |

| P2         | 0     |       | 1      | <b>P</b> 7 |       |       |        |

| <b>P3</b>  | 0     |       | 1      | P8         |       |       |        |

| P4         |       |       |        | <b>P9</b>  |       |       |        |

| <b>P</b> 5 |       |       |        | P10        |       |       |        |

Register renaming in motion R I AR LSQ MEM WB

INT

|   |      | <del>-</del> - |   |   |     |     |   |

|---|------|----------------|---|---|-----|-----|---|

| 1 | ld   | X6,0(X10)      | R | I | AR  | LSQ | ľ |

| 2 | add  | X7,X6,X12      |   | R | - 1 | ı   |   |

| 3 | sd   | X7,0(X10)      |   |   | R   | ı   |   |

| 4 | addi | X10,X10,8      |   |   |     | R   |   |

1d X6,0(X10)

bne

(5)

X10, X5, LOOP

- ② add X7,X6,X12

- 8 sd X7,0(X10)

- addi X10,X10,8

- 10 bne X10, X5, LOOP

|    | Ren        | amed | instruction |

|----|------------|------|-------------|

| 1  | <b>1</b> d | P1,  | 0(X10)      |

| 2  | add        | P2,  | P1, X12     |

| 3  | sd         | P2,  | 0(X10)      |

| 4  | addi       | P3,  | X10, 8      |

| 5  | bne        | Р3,  | X5, LOOP    |

| 6  | <b>1</b> d | P4,  | 0(P3)       |

| 7  |            |      |             |

| 8  |            |      |             |

| 9  |            |      |             |

| 10 |            |      |             |

|           | Physical Register |

|-----------|-------------------|

| <b>X5</b> |                   |

| <b>X6</b> | P1                |

| <b>X7</b> | P2                |

| X10       | Р3                |

| X12       |                   |

|            | Valid | Value In use |            | Valid | Value | In use |

|------------|-------|--------------|------------|-------|-------|--------|

| P1         | 1     | 1            | P6         |       |       |        |

| P2         | 0     | 1            | <b>P</b> 7 |       |       |        |

| <b>P3</b>  | 0     | 1            | P8         |       |       |        |

| P4         | 0     | 1            | <b>P</b> 9 |       |       |        |

| <b>P</b> 5 |       |              | P10        |       |       |        |

Register renaming in motion R I AR LSQ MEM WB

INT

R

R

R

INT

WB

R

| 1 | ld  | X6,0(X10) | R |

|---|-----|-----------|---|

| 2 | add | X7,X6,X12 |   |

| 3 | sd  | X7,0(X10) |   |

- @ addi X10,X10,8

- 5 bne X10,X5,L00P

- © ld X6,0(X10)

- ② add X7,X6,X12

- sd X7,0(X10)

- ⊚ addi X10,X10,8

- ① bne X10, X5, LOOP

|     | Ren           | amed | instruction       |

|-----|---------------|------|-------------------|

| 1 - | <del>1d</del> | P1,  | <del>0(X10)</del> |

| 2   | add           | P2,  | P1, X12           |

| 3   | sd            | P2,  | 0(X10)            |

| 4   | addi          | P3,  | X10, 8            |

| 5   | bne           | P3,  | X5, LOOP          |

| 6   | <b>1</b> d    | P4,  | 0(P3)             |

| 7   | add           | P5,  | P1, X12           |

| 8   |               |      |                   |

| 9   |               |      |                   |

| 10  |               |      |                   |

|            | Physical Register |

|------------|-------------------|

| <b>X</b> 5 |                   |

| <b>X6</b>  | P1                |

| <b>X7</b>  | P5                |

| X10        | Р3                |

| X12        |                   |

|           | Valid | Value | In use |            | Valid | Value | In use |

|-----------|-------|-------|--------|------------|-------|-------|--------|

| P1        | 1     |       | 1      | P6         |       |       |        |

| P2        | 0     |       | 1      | <b>P</b> 7 |       |       |        |

| <b>P3</b> | 1     |       | 1      | P8         |       |       |        |

| P4        | 0     |       | 1      | <b>P</b> 9 |       |       |        |

| P5        | 0     |       | 1      | P10        |       |       |        |

| 1 | ld  | X6,0(X10) |  |

|---|-----|-----------|--|

| 2 | add | X7,X6,X12 |  |

| 3 | sd  | X7,0(X10) |  |

- addi X10,X10,8

- ⑤ bne X10,X5,L00P

- © ld X6,0(X10)

- ② add X7,X6,X12

- 8 sd X7,0(X10)

- 9 addi X10,X10,8

- ① bne X10, X5, LOOP

| Renamed instruction |               |     |                   |  |  |  |  |

|---------------------|---------------|-----|-------------------|--|--|--|--|

| 1 -                 | <del>1d</del> | P1, | <del>0(X10)</del> |  |  |  |  |

| 2                   | add           | P2, | P1, X12           |  |  |  |  |

| 3                   | sd            | P2, | 0(X10)            |  |  |  |  |

| 4 -                 | addi          | P3, | X10, 8            |  |  |  |  |

| 5                   | bne           | Р3, | X5, LOOP          |  |  |  |  |

| 6                   | <b>1</b> d    | P4, | 0(P3)             |  |  |  |  |

| 7                   | add           | P5, | P1, X12           |  |  |  |  |

| 8                   | sd            | P5, | 0(P3)             |  |  |  |  |

| 9                   |               |     |                   |  |  |  |  |

| 10                  |               |     |                   |  |  |  |  |

| ı | AR | LSQ | MEM | WB  |     |    |

|---|----|-----|-----|-----|-----|----|

| R | 1  | ı   | - 1 | 1   | INT | WB |

|   | R  | I   | I   | 1   | I   | I  |

|   |    | R   | - 1 | INT | WB  |    |

|   |    |     | R   | -1  | I   | BR |

|   |    |     |     | R   | 1   | AR |

|   |    |     |     |     | R   | ı  |

|   |    |     |     |     |     | R  |

|   |    |     |     |     |     |    |

| Physical Register |    |  |  |  |  |  |

|-------------------|----|--|--|--|--|--|

| <b>X5</b>         |    |  |  |  |  |  |

| <b>X6</b>         | P1 |  |  |  |  |  |

| <b>X7</b>         | P5 |  |  |  |  |  |

| X10               | Р3 |  |  |  |  |  |

| X12               |    |  |  |  |  |  |

|            | Valid | Value In use |     | Valid | Value | In use |

|------------|-------|--------------|-----|-------|-------|--------|

| P1         | 1     | 1            | P6  |       |       |        |

| P2         | 1     | 1            | P7  |       |       |        |

| <b>P3</b>  | 1     | 1            | P8  |       |       |        |

| P4         | 0     | 1            | P9  |       |       |        |

| <b>P</b> 5 | 0     | 1            | P10 |       |       |        |

| 1 | ld | X6,0(X10) |

|---|----|-----------|

|   |    |           |

- ② add X7,X6,X12

- 3 sd X7,0(X10)

- addi X10,X10,8

- ⑤ bne X10,X5,L00P

- 1d X6,0(X10)

- ② add X7,X6,X12

- 8 sd X7,0(X10)

- 9 addi X10,X10,8

- ① bne X10, X5, LOOP

|     | Ren           | amed instruction | on |

|-----|---------------|------------------|----|

| 1 - | <del>ld</del> | P1, 0(X10)       |    |

| 2 - | add           | P2, P1, X12      |    |

| 3   | sd            | P2, 0(X10)       |    |

| 4 - | addi          | P3, X10, 8       |    |

| 5   | bne           | P3, X5, L00      | )P |

| 6   | <b>1</b> d    | P4, 0(P3)        |    |

| 7   | add           | P5, P1, X12      | 2  |

| 8   | sd            | P5, 0(P3)        |    |

| 9   | addi          | P6, P3, 8        |    |

| 10  |               |                  |    |

|     |     |     |     |     |     |    | <u>UL</u> |

|-----|-----|-----|-----|-----|-----|----|-----------|

|     |     |     | WB  | MEM | LSQ | AR | 1         |

|     | WB  | INT | -1  | I   | ı   | I  | R         |

| AR  | I   | 1   | 1.  | ı   | ı   | R  |           |

|     |     | WB  | INT | - 1 | R   |    |           |

| WB  | BR  | 1   | - 1 | R   |     |    |           |

| LSQ | AR  | T.  | R   |     |     |    |           |

| I   | l I | R   |     |     |     |    |           |

| I   | R   |     |     |     |     |    |           |

| R   |     |     |     |     |     |    |           |

|     |     |     |     |     |     |    |           |

|            | Physical Register |

|------------|-------------------|

| <b>X</b> 5 |                   |

| <b>X6</b>  | P1                |

| <b>X7</b>  | P5                |

| X10        | Р3                |

| X12        |                   |

|           | Valid | Value In use |            | Valid | Value | In use |

|-----------|-------|--------------|------------|-------|-------|--------|

| P1        | 1     | 1            | P6         | 0     |       | 1      |

| P2        | 1     | 1            | <b>P</b> 7 |       |       |        |

| <b>P3</b> | 1     | 1            | P8         |       |       |        |

| P4        | 0     | 1            | <b>P</b> 9 |       |       |        |

| <b>P5</b> | 0     | 1            | P10        |       |       |        |

| 1 | ld | X6,0(X10) |

|---|----|-----------|

| U | Τu | YO'A(YTA) |

- add X7, X6, X12

- 3 sd X7,0(X10)

- addi X10,X10,8

- ⑤ bne X10,X5,L00P

- © ld X6,0(X10)

- ② add X7, X6, X12

- ® sd X7,0(X10)

- addi X10,X10,8

- ① bne X10, X5, LOOP

|     | Ren           | amed instruction |

|-----|---------------|------------------|

| 1 - | <del>ld</del> | P1, 0(X10)       |

| 2 - | add           | P2, P1, X12      |

| 3   | sd            | P2, 0(X10)       |

| 4 - | addi          | P3, X10, 8       |

| 5 - | bne           | P3, X5, L00P     |

| 6   | 1d            | P4, 0(P3)        |

| 7   | add           | P5, P1, X12      |

| 8   | sd            | P5, 0(P3)        |

| 9   | addi          | P6, P3, 8        |

| 10  | bne           | P6, 0(X10)       |

|   |    |     |     |     | י כי |    |     |     |

|---|----|-----|-----|-----|------|----|-----|-----|

| I | AR | LSQ | MEM | WB  |      |    |     |     |

| R | 1  | I   | - 1 | - 1 | INT  | WB |     |     |

|   | R  | I   | I   | ı   |      | ı  | AR  | LSQ |

|   |    | R   | ı   | INT | WB   |    |     |     |

|   |    |     | R   | -1  | ı    | BR | WB  |     |

|   |    |     |     | R   | ı    | AR | LSQ | MEM |

|   |    |     |     |     | R    | ı  | 1   | - 1 |

|   |    |     |     |     |      | R  | - 1 | 1   |

|   |    |     |     |     |      |    | R   | - 1 |

|   |    |     |     |     |      |    |     |     |

|           | Physical Register |

|-----------|-------------------|

| <b>X5</b> |                   |

| <b>X6</b> | P1                |

| <b>X7</b> | P5                |

| X10       | Р3                |

| X12       |                   |

|            | Valid | Value In use |            | Valid | Value | In use |

|------------|-------|--------------|------------|-------|-------|--------|

| P1         | 1     | 1            | P6         | 0     |       | 1      |

| P2         | 1     | 1            | <b>P</b> 7 |       |       |        |

| <b>P</b> 3 | 1     | 1            | P8         |       |       |        |

| P4         | 0     | 1            | <b>P</b> 9 |       |       |        |

| <b>P</b> 5 | 0     | 1            | P10        |       |       |        |

| ① ld | X6,0(X10) |

|------|-----------|

|------|-----------|

- ② add X7,X6,X12

- 3 sd X7,0(X10)

- addi X10,X10,8

- ⑤ bne X10,X5,L00P

- 1d X6,0(X10)

- ② add X7,X6,X12

- 8 sd X7,0(X10)

- addi X10,X10,8

- 10 bne X10, X5, LOOP

|     | Ren           | amed | instruction       |

|-----|---------------|------|-------------------|

| 1 - | <del>1d</del> | P1,  | <del>0(X10)</del> |

| 2 - | add           | P2,  | P1, X12           |

| 3   | sd            | P2,  | 0(X10)            |

| 4 - | addi          | P3,  | X10, 8            |

| 5 - | bne           | P3,  | X5, L00P          |

| 6   | 1d            | P4,  | 0(P3)             |

| 7   | add           |      | P1, X12           |

| 8   | sd            |      | 0(P3)             |

| 9   | addi          | P6,  | P3, 8             |

| 10  | bne           | P6,  | 0(X10)            |

| 1 | AR  | LSQ | MEM | WB  |     |    |     |     |     |

|---|-----|-----|-----|-----|-----|----|-----|-----|-----|

| R | 1.0 | - 1 | - 1 | - 1 | INT | WB |     |     |     |

|   | R   | ı   | ı   | ı   | - 1 | ı  | AR  | LSQ | MEM |

|   |     | R   | 1   | INT | WB  |    |     |     |     |

|   |     |     | R   | 1   | 1   | BR | WB  |     |     |

|   |     |     |     | R   | ı   | AR | LSQ | MEM | WB  |

|   |     |     |     |     | R   | ı  | ı   | - 1 | 1   |

|   |     |     |     |     |     | R  | - 1 | - 1 | - 1 |

|   |     |     |     |     |     |    | R   | - 1 | INT |

|   |     |     |     |     |     |    |     | D   |     |

|            | Physical Register |

|------------|-------------------|

| <b>X</b> 5 |                   |

| <b>X6</b>  | P1                |

| <b>X7</b>  | P5                |

| X10        | Р3                |

| X12        |                   |

|            | Valid | Value In u | ise  | Valid | Value | In use |

|------------|-------|------------|------|-------|-------|--------|

| P1         | 1     | 1          | P6   | 0     |       | 1      |

| P2         | 1     | 1          | . P7 |       |       |        |

| <b>P</b> 3 | 1     | 1          | . P8 |       |       |        |

| P4         | 1     | 1          | . P9 |       |       |        |

| <b>P</b> 5 | 0     | 1          | P10  |       |       |        |

| 1 | ld | X6,0(X10) |

|---|----|-----------|

|   |    | - , - ,   |

- add X7, X6, X12

- 3 sd X7,0(X10)

- addi X10,X10,8

- ⑤ bne X10,X5,L00P

- © ld X6,0(X10)

- ② add X7,X6,X12

- 8 sd X7,0(X10)

- addi X10,X10,8

- 10 bne X10, X5, LOOP

|     | Ren           | amed instruction |

|-----|---------------|------------------|

| 1 - | <del>1d</del> | P1, 0(X10)       |

| 2 - | add           | P2, P1, X12      |

| 3 - | sd            | P2, 0(X10)       |

| 4 = | addi          | P3, X10, 8       |

| 5 - | bne           | P3, X5, L00P     |

| 6 - | 1d            | P4, 0(P3)        |

| 7   | add           | P5, P1, X12      |

| 8   | sd            | P5, 0(P3)        |

| 9   | addi          | P6, P3, 8        |

| 10  | bne           | P6, 0(X10)       |

|     |     |     |     |    |     | WB  | MEM | LSQ | AR | 1 |

|-----|-----|-----|-----|----|-----|-----|-----|-----|----|---|

|     |     |     |     | WB | INT | -1  | I   | ı   | 1  | R |

|     | MEM | LSQ | AR  | 1  | 1   | -1  | I   | ı   | R  |   |

|     |     |     |     |    | WB  | INT | ı   | R   |    |   |

|     |     |     | WB  | BR | 1   | 1   | R   |     |    |   |

|     | WB  | MEM | LSQ | AR | - 1 | R   |     |     |    |   |

| INT | - 1 | - 1 | - 1 | ı  | R   |     |     |     |    |   |

| - 1 | - 1 | 1   | ı   | R  |     |     |     |     |    |   |

| WB  | INT | 1   | R   |    |     |     |     |     |    |   |

|     |     |     |     |    |     |     |     |     |    |   |

|           | Physical Register |

|-----------|-------------------|

| <b>X5</b> |                   |

| <b>X6</b> | P1                |

| <b>X7</b> | P5                |

| X10       | Р3                |

| X12       |                   |

|           | Valid | Value I | In use |            | Valid | Value | In use |

|-----------|-------|---------|--------|------------|-------|-------|--------|

| P1        | 1     |         | 1      | P6         | 1     |       | 1      |

| P2        | 1     |         | 1      | <b>P</b> 7 |       |       |        |

| <b>P3</b> | 1     |         | 1      | P8         |       |       |        |

| P4        | 1     |         | 1      | <b>P</b> 9 |       |       |        |

| P5        | 0     |         | 1      | P10        |       |       |        |

| X6,0 | (X10) |

|------|-------|

|      | X6,0  |

- ② add X7,X6,X12

- 3 sd X7,0(X10)

- addi X10,X10,8

- 5 bne X10,X5,L00P

- © ld X6,0(X10)

- ② add X7, X6, X12

- ® sd X7,0(X10)

- addi X10,X10,8

- 10 bne X10, X5, LOOP

|     | Ren           | amed instruction |

|-----|---------------|------------------|

| 1 - | <del>1d</del> | P1, 0(X10)       |

| 2 - | add           | P2, P1, X12      |

| 3 - | sd            | P2, 0(X10)       |

| 4 - | addi          | P3, X10, 8       |

| 5 - | bne           | P3, X5, LOOP     |

| 6 - | 1d            | P4, 0(P3)        |

| 7   | add           | P5, P1, X12      |

| 8   | sd            | P5, 0(P3)        |

| 9 - | addi          | Pó, P3, 8        |

| 10  | bne           | P6, 0(X10)       |

|     |     |     |     |     |     | WB  | MEM | LSQ | AR  | 1 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---|

|     |     |     |     | WB  | INT | 1.  | ı   | I   | - 1 | R |

|     | MEM | LSQ | AR  | - 1 | - 1 | - 1 | I   |     | R   |   |

|     |     | _   |     |     | WB  | INT | ı   | R   |     |   |

|     |     |     | WB  | BR  | - 1 | 1.0 | R   |     |     |   |

|     | WB  | MEM | LSQ | AR  | - 1 | R   |     |     |     |   |

| INT | 1   | I   | I   | - 1 | R   |     |     |     |     |   |

| I   | I   | 1   | ı   | R   |     |     |     |     |     |   |

|     |     |     |     |     |     |     |     |     |     |   |

|            | Physical Register |

|------------|-------------------|

| <b>X</b> 5 |                   |

| <b>X6</b>  | P1                |

| <b>X7</b>  | P5                |

| X10        | Р3                |

| X12        |                   |

|            | Valid | Value In use | <b>e</b> | Valid | Value | In use |

|------------|-------|--------------|----------|-------|-------|--------|

| P1         | 1     | 1            | P6       | 1     |       | 1      |

| P2         | 1     | 1            | P7       |       |       |        |

| <b>P</b> 3 | 1     | 1            | P8       |       |       |        |

| P4         | 1     | 1            | P9       |       |       |        |

| <b>P</b> 5 | 1     | 1            | P10      |       |       |        |

INT

WB

R

WB

BR

- ② add X7,X6,X12

- 3 sd X7,0(X10)

- addi X10,X10,8

- ⑤ bne X10,X5,L00P

- 1d X6,0(X10)

- ② add X7, X6, X12

- sd X7,0(X10)

- 9 addi X10,X10,8

- 10 bne X10, X5, LOOP

|            | Ren           | amed | instruction       |

|------------|---------------|------|-------------------|

| 1 -        | <del>1d</del> | P1,  | <del>0(X10)</del> |

| 2 -        | add           | P2,  | P1, X12           |

| 3 =        | sd            | P2,  | 0(X10)            |

| 4 =        | addi          | D2   | X10, 8            |

| 5 <b>-</b> | hme           | P3,  | VE LOOP           |

| 6 -        | 7.1           | ,    | 0/00)             |

| 7 -        | add           | DE   | D1 V12            |

| •          |               | DE   | 0(02)             |

| 8          | sd            | P5,  | 0(P3)             |

| 9 -        | auuı          | PO,  | P3, 0             |

| 10         | bne           | P6,  | 0(X10)            |

|         |     |    |     | WB  | MEM | LSQ | AR | -1 |

|---------|-----|----|-----|-----|-----|-----|----|----|

|         |     | WB | INT | - 1 | I   | ı   | 1  | R  |

| LSQ MEM | AR  | I  | ı   | ı   |     |     | R  |    |

|         |     |    | WB  | INT | ı   | R   |    |    |

|         | WB  | BR | ı   | -1  | R   |     |    |    |

| MEM WB  | LSQ | AR | - 1 | R   |     |     |    |    |

| 1 1     | - 1 | I  | R   |     |     |     |    |    |

R

R

|            | Physical Register |

|------------|-------------------|

| <b>X</b> 5 |                   |

| <b>X6</b>  | P1                |

| <b>X7</b>  | P5                |

| X10        | Р3                |

| X12        |                   |

|           | Valid | Value | In use |            | Valid | Value | In use |

|-----------|-------|-------|--------|------------|-------|-------|--------|

| P1        | 1     |       | 1      | P6         | 1     |       | 1      |

| P2        | 1     |       | 1      | <b>P</b> 7 |       |       |        |

| <b>P3</b> | 1     |       | 1      | P8         |       |       |        |

| P4        | 1     |       | 1      | <b>P</b> 9 |       |       |        |

| P5        | 1     |       | 1      | P10        |       |       |        |

INT

INT

WB

WB

BR

AR

WB

| ① ld | X6,0(X10) |

|------|-----------|

|------|-----------|

- ② add X7,X6,X12

- 3 sd X7,0(X10)

- addi X10,X10,8

- ⑤ bne X10,X5,L00P

- © 1d X6,0(X10)

- ② add X7, X6, X12

- sd X7,0(X10)

- addi X10,X10,8

- 10 bne X10, X5, LOOP

|     | Ren            | named instruction |   |

|-----|----------------|-------------------|---|

| 1 - | <del>1d</del>  | P1, 0(X10)        |   |

| 2 - | add            | P2, P1, X12       |   |

| 3 - | sd             | P2, 0(X10)        |   |

| 4 - | addi           | P3, X10, 8        |   |

| 5 - | bne            | P3, X5, L00P      |   |

| 6 - | <del>1</del> d | P4, 0(P3)         |   |

| 7 - | add            | P5, P1, X12       | _ |

| 8   | sd             | P5, 0(P3)         |   |

| 9 - | addi           | P6, P3, 8         |   |

| 10- | bne            | P6, 9(X19)        |   |

| I | AR  | LSQ |     | WB  |     |    |     |     |     |  |

|---|-----|-----|-----|-----|-----|----|-----|-----|-----|--|

| R | 1.0 | ı   | - 1 | 11  | INT | WB |     |     |     |  |

|   | R   | I   | ı   | 1.  | 1   | ı  | AR  | LSQ | MEM |  |

|   |     | R   | 1   | INT | WB  |    |     |     |     |  |

|   |     |     | R   | 1.0 | - 1 | BR | WB  |     |     |  |

|   |     |     |     | R   | ı   | AR | LSQ | MEM | WB  |  |

|   |     |     |     |     | R   | ı  | ı   | ı   | ı   |  |

R

R

|            | Physical Register |

|------------|-------------------|

| <b>X</b> 5 |                   |

| <b>X6</b>  | P1                |

| <b>X7</b>  | P5                |

| X10        | Р3                |

| X12        |                   |

|           | Valid | Value | In use |            | Valid | Value | In use |

|-----------|-------|-------|--------|------------|-------|-------|--------|

| P1        | 1     |       | 1      | P6         | 1     |       | 1      |

| P2        | 1     |       | 1      | <b>P</b> 7 |       |       |        |

| <b>P3</b> | 1     |       | 1      | P8         |       |       |        |

| P4        | 1     |       | 1      | P9         |       |       |        |

| <b>P5</b> | 1     |       | 1      | P10        |       |       |        |

INT

INT

WB

WB

BR

LS

AR

WB

| 1 | ld  | X6,0(X10)   |

|---|-----|-------------|

| 2 | add | X7, X6, X12 |

- sd X7,0(X10)

- addi X10,X10,8

- X10,X5,L00P

- X6,0(X10)ld

- X7, X6, X12 add

- X7,0(X10)sd

- addi X10,X10,8

- 10 bne

P5, 0(P3)

D6 Q(Y1Q)

| R | I | AR | LSQ | MEM | WB  |     |    |     |     |     |

|---|---|----|-----|-----|-----|-----|----|-----|-----|-----|

|   | R | -1 | - 1 |     | -1  | INT | WB |     |     |     |

|   |   | R  | ı   | ı   | 1.0 | 1   | ı  | AR  | LSQ | MEM |

|   |   |    | R   | ı   | INT | WB  |    |     |     |     |

|   |   |    |     | R   | - 1 | - 1 | BR | WB  |     |     |

|   |   |    |     |     | R   |     | AR | LSQ | MEM | WB  |

|   |   |    |     |     |     |     |    |     |     |     |

R

R

## Takes 12 cycles to X10, X5, LOOP issue all instructions

| Ren           | amed | instruction       |            | Physical Register |

|---------------|------|-------------------|------------|-------------------|

| <del>1d</del> | P1,  | <del>0(X10)</del> | <b>X</b> 5 |                   |

| add           | P2,  | P1, X12           | <b>X</b> 6 | P1                |

| <del>3d</del> | P2,  | 0(X10)            | <b>X7</b>  | P5                |

| addi          | P3,  | X10, 8            | X10        | Р3                |

| bne           | P3,  | X5, LOOP          | X12        |                   |

| 14            | P4,  | 0(P3)             | N12        |                   |

|           | Valid | Value | In use |            | Valid | Value | In use |

|-----------|-------|-------|--------|------------|-------|-------|--------|

| P1        | 1     |       | 1      | P6         | 1     |       | 1      |

| P2        | 1     |       | 1      | <b>P</b> 7 |       |       |        |

| <b>P3</b> | 1     |       | 1      | P8         |       |       |        |

| P4        | 1     |       | 1      | <b>P</b> 9 |       |       |        |

| P5        | 1     |       | 1      | P10        |       |       |        |

INT

INT

WB

WB

BR

AR

WB

Through data flow graph analysis

- ② add X7, X6, X12

- 3 sd X7,0(X10)

- @ addi X10,X10,8

- bne X10, X5, L00P

- ld X6,0(X10)

- ② add X7, X6, X12

- 8 sd X7,0(X10)

- addi X10,X10,8

- 10 bne X10, X5, L00P

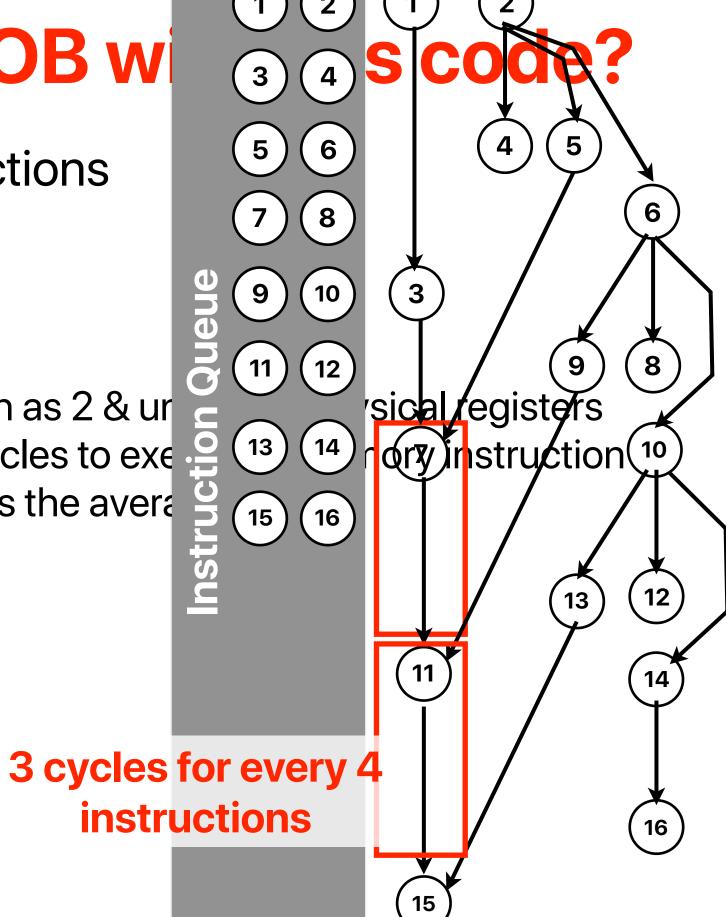

INT — 2 cycles for depending instruction to start MEM — 4 cycles for the depending instruction to start MUL/DIV — 4 cycles for the depending instruction to start BR — 2 cycles to resolve

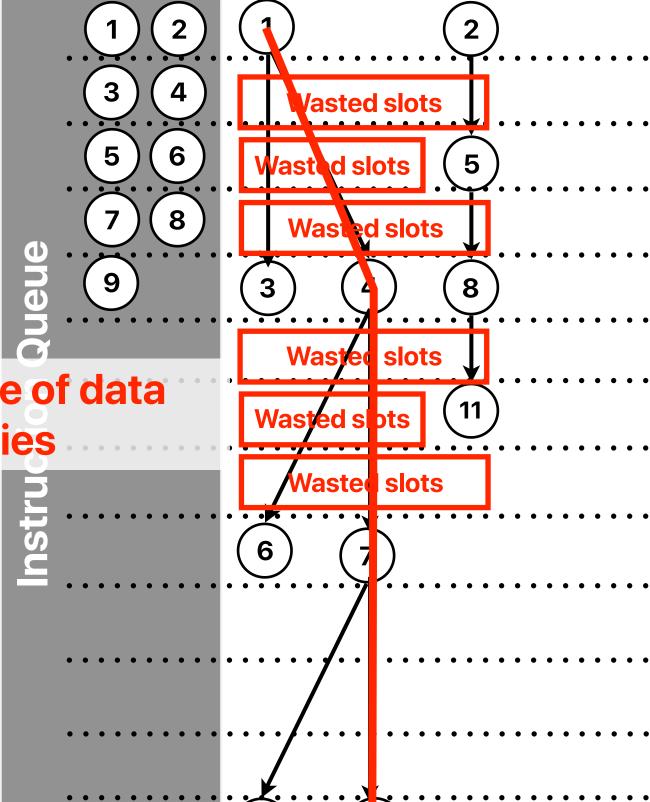

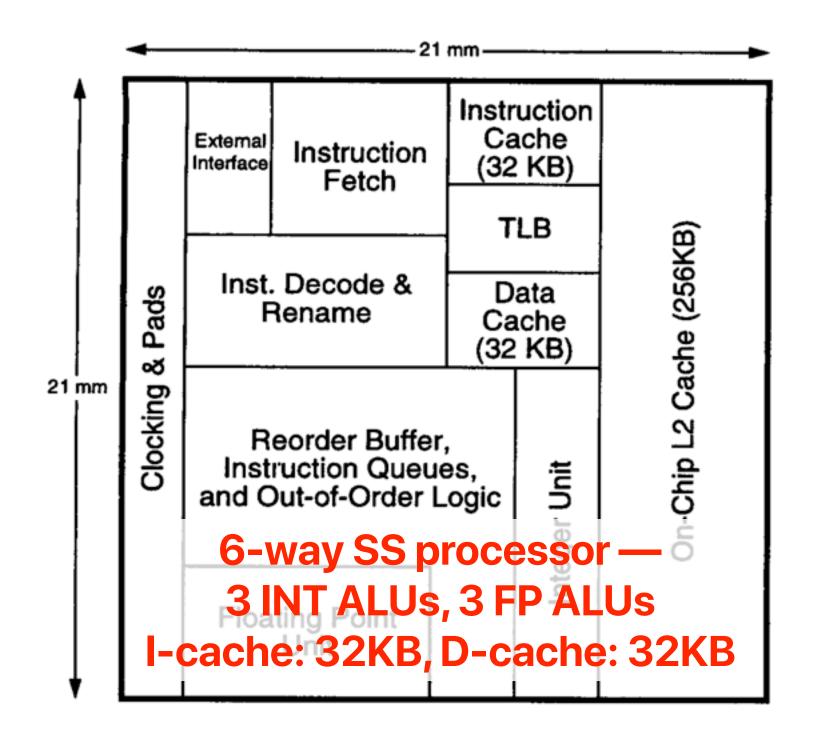

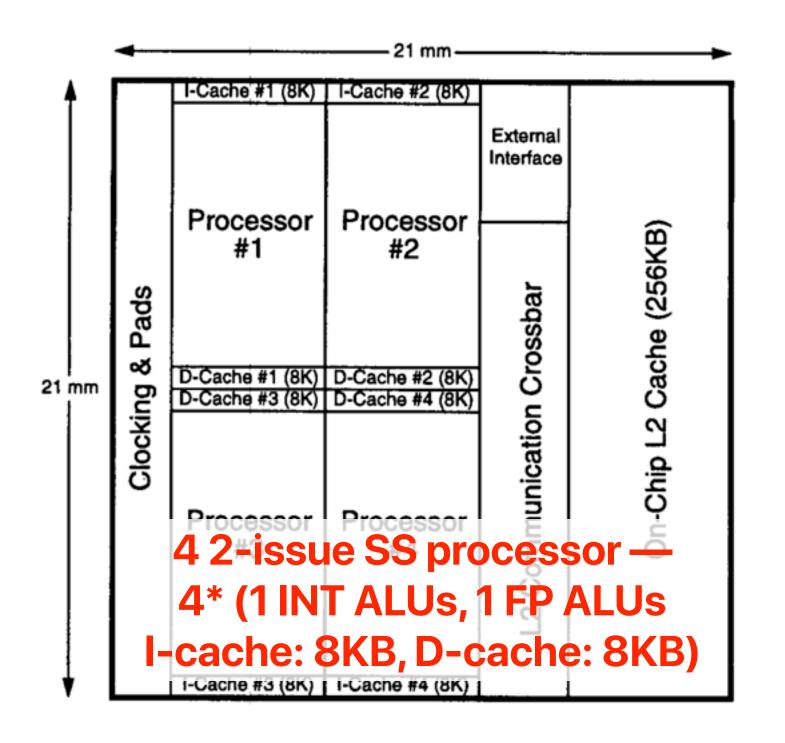

## Super Scalar

## Superscalar

- Since we have more functional units now, we should fetch/ decode more instructions each cycle so that we can have more instructions to issue!

- Super-scalar: fetch/decode/issue more than one instruction each cycle

- Fetch width: how many instructions can the processor fetch/ decode each cycle

- Issue width: how many instructions can the processor issue each cycle

Overview of a processor supporting register renaming Fetch/decode instruction physical Renaming **Unresolved** X1 register # What if we widen the **Branch** logic **Physical** pipeline to fetch/issue Register Registers two instructions at the mapping table nstruction same time? Queue Floating-**Address** Integer Floating-**Branch Point Mul/Div Point Adder** Resolution **ALU Store** Load **Memory** Queue Queue Address Data

```

① ld X6,0(X10)

```

- @ add X7,X6,X12

- 3 sd X7,0(X10)

- addi X10,X10,8

- bne X10, X5, L00P

- © ld X6,0(X10)

- ② add X7,X6,X12

- 8 sd X7,0(X10)

- 9 addi X10,X10,8

- 10 bne X10, X5, LOOP

|    | Renamed instruction |     |            |     |  |  |  |  |  |  |  |

|----|---------------------|-----|------------|-----|--|--|--|--|--|--|--|

| 1  | <b>1</b> d          | P1, | <b>0(X</b> | 10) |  |  |  |  |  |  |  |

| 2  | add                 | P2, | P1,        | X12 |  |  |  |  |  |  |  |

| 3  |                     |     |            |     |  |  |  |  |  |  |  |

| 4  |                     |     |            |     |  |  |  |  |  |  |  |

| 5  |                     |     |            |     |  |  |  |  |  |  |  |

| 6  |                     |     |            |     |  |  |  |  |  |  |  |

| 7  |                     |     |            |     |  |  |  |  |  |  |  |

| 8  |                     |     |            |     |  |  |  |  |  |  |  |

| 9  |                     |     |            |     |  |  |  |  |  |  |  |

| 10 |                     |     |            |     |  |  |  |  |  |  |  |

|            | Physical Register |

|------------|-------------------|

| <b>X</b> 5 |                   |

| <b>X6</b>  | P1                |

| <b>X7</b>  | P2                |

| X10        |                   |

| X12        |                   |

|            | Valid | Value | In use |           | Valid | Value | In use |

|------------|-------|-------|--------|-----------|-------|-------|--------|

| P1         | 0     |       | 1      | P6        |       |       |        |

| P2         | 0     |       | 1      | <b>P7</b> |       |       |        |

| <b>P</b> 3 |       |       |        | P8        |       |       |        |

| P4         |       |       |        | <b>P9</b> |       |       |        |

| <b>P</b> 5 |       |       |        | P10       |       |       |        |

1d X6,0(X10)

add X7,X6,X12

sd X7,0(X10)

addi X10,X10,8

- 5 bne X10,X5,L00P

- © ld X6,0(X10)

- ② add X7,X6,X12

- sd X7,0(X10)

- 9 addi X10,X10,8

- ① bne X10, X5, LOOP

|    | Ren        | amed | instruction |  |

|----|------------|------|-------------|--|

| 1  | <b>1</b> d | P1,  | 0(X10)      |  |

| 2  | add        | P2,  | P1, X12     |  |

| 3  | sd         | P2,  | 0(X10)      |  |

| 4  | addi       | P3,  | X10, 8      |  |

| 5  |            |      |             |  |

| 6  |            |      |             |  |

| 7  |            |      |             |  |

| 8  |            |      |             |  |

| 9  |            |      |             |  |

| 10 |            |      |             |  |

|           | Physical Register |

|-----------|-------------------|

| <b>X5</b> |                   |

| <b>X6</b> | P1                |

| <b>X7</b> | P2                |

| X10       | Р3                |

| X12       |                   |

|            | Valid | Value | In use |            | Valid | Value | In use |

|------------|-------|-------|--------|------------|-------|-------|--------|

| P1         | 0     |       | 1      | P6         |       |       |        |

| P2         | 0     |       | 1      | <b>P</b> 7 |       |       |        |

| <b>P</b> 3 | 0     |       | 1      | P8         |       |       |        |

| P4         |       |       |        | P9         |       |       |        |

| <b>P</b> 5 |       |       |        | P10        |       |       |        |

| 1 | ld   | X6,0(X10)   | R | - 1 | AR  |

|---|------|-------------|---|-----|-----|

| 2 | add  | X7,X6,X12   | R | 1   | - 1 |

| 3 | sd   | X7,0(X10)   |   | R   | - 1 |

| 4 | addi | X10,X10,8   |   | R   | - 1 |

| 5 | bne  | X10,X5,L00P |   |     | R   |

| 6 | ld   | X6,0(X10)   |   |     | R   |

| 7 | add | X7 | . X6 | . X12 |

|---|-----|----|------|-------|

- sd X7,0(X10)

- 9 addi X10,X10,8

- ① bne X10,X5,L00P

| Renamed instruction |            |     |          |  |  |  |

|---------------------|------------|-----|----------|--|--|--|

| 1                   | <b>1</b> d | P1, | 0(X10)   |  |  |  |

| 2                   | add        | P2, | P1, X12  |  |  |  |

| 3                   | sd         | P2, | 0(X10)   |  |  |  |

| 4                   | addi       | P3, | X10, 8   |  |  |  |

| 5                   | bne        | P3, | X5, LOOP |  |  |  |

| 6                   | <b>1</b> d | P4, | 0(P3)    |  |  |  |

| 7                   |            |     |          |  |  |  |

| 8                   |            |     |          |  |  |  |

| 9                   |            |     |          |  |  |  |

| 10                  |            |     |          |  |  |  |

|           | Physical Register |

|-----------|-------------------|

| <b>X5</b> |                   |

| <b>X6</b> | P1                |

| <b>X7</b> | P2                |

| X10       | Р3                |

| X12       |                   |

|            | Valid | Value In use |            | Valid | Value | In use |

|------------|-------|--------------|------------|-------|-------|--------|

| P1         | 0     | 1            | P6         |       |       |        |

| P2         | 0     | 1            | <b>P</b> 7 |       |       |        |

| <b>P3</b>  | 0     | 1            | P8         |       |       |        |

| P4         | 0     | 1            | P9         |       |       |        |

| <b>P</b> 5 |       |              | P10        |       |       |        |

```

R

AR

AQ

X6,0(X10)

ld

X7,X6,X12

add

X7,0(X10)

sd

addi X10,X10,8

INT

bne X10, X5, LOOP

```

| 6  | ld   | X6,0(X10)   |

|----|------|-------------|

| 7  | add  | X7,X6,X12   |

| 8  | sd   | X7,0(X10)   |

| 9  | addi | X10,X10,8   |

| 10 | bne  | X10,X5,LOOP |

|    | Ren        | amed | instruction |

|----|------------|------|-------------|

| 1  | <b>1</b> d | P1,  | 0(X10)      |

| 2  | add        | P2,  | P1, X12     |

| 3  | sd         | P2,  | 0(X10)      |

| 4  | addi       | P3,  | X10, 8      |

| 5  | bne        | P3,  | X5, LOOP    |

| 6  | <b>1</b> d | P4,  | 0(P3)       |

| 7  | add        | P5,  | P1, X12     |

| 8  | sd         | P5,  | 0(P3)       |

| 9  |            |      |             |

| 10 |            |      |             |

| Physical Register |    |  |  |  |  |  |

|-------------------|----|--|--|--|--|--|

| <b>X</b> 5        |    |  |  |  |  |  |

| <b>X6</b>         | P1 |  |  |  |  |  |

| <b>X7</b>         | P5 |  |  |  |  |  |

| X10               | Р3 |  |  |  |  |  |

| X12               |    |  |  |  |  |  |

R

R

|            | Valid | Value I | n use |            | Valid | Value | In use |

|------------|-------|---------|-------|------------|-------|-------|--------|

| P1         | 0     |         | 1     | P6         |       |       |        |

| P2         | 0     |         | 1     | <b>P</b> 7 |       |       |        |

| <b>P3</b>  | 0     |         | 1     | P8         |       |       |        |

| P4         | 0     |         | 1     | <b>P</b> 9 |       |       |        |

| <b>P</b> 5 | 0     |         | 1     | P10        |       |       |        |

MEM

WB

R

R

|   |      | <del></del> - |   |   |     |     |

|---|------|---------------|---|---|-----|-----|

| 1 | ld   | X6,0(X10)     | R | I | AR  | AQ  |

| 2 | add  | X7,X6,X12     | R | I | 1   | - 1 |

| 3 | sd   | X7,0(X10)     |   | R | - 1 | - 1 |

| 4 | addi | X10.X10.8     |   | R |     | INT |

- 5 bne X10,X5,L00P

- © ld X6,0(X10)

- ② add X7,X6,X12

- 8 sd X7,0(X10)

- addi X10,X10,8

- 10 bne X10, X5, LOOP

|    | Ren        | amed ins | struction |

|----|------------|----------|-----------|

| 1  | <b>1</b> d | P1, 0(   | X10)      |

| 2  | add        | P2, P1   | ., X12    |

| 3  | sd         | P2, 0(   | X10)      |

| 4  | addi       | P3, X1   | .0, 8     |

| 5  | bne        | P3, X5   | , LOOP    |

| 6  | <b>1</b> d | P4, 0(   | P3)       |

| 7  | add        | P5, P1   | ., X12    |

| 8  | sd         | P5, 0(   | P3)       |

| 9  | addi       | P6, P3   | 8, 8      |

| 10 | bne        | P6, 0(   | X10)      |

|           | Physical Register |

|-----------|-------------------|

| <b>X5</b> |                   |

| <b>X6</b> | P1                |

| <b>X7</b> | P5                |

| X10       | Р3                |

| X12       |                   |

|           | Valid | Value | In use |            | Valid | Value | In use |

|-----------|-------|-------|--------|------------|-------|-------|--------|

| P1        | 0     |       | 1      | P6         |       |       |        |

| P2        | 0     |       | 1      | <b>P</b> 7 |       |       |        |

| <b>P3</b> | 1     |       | 1      | P8         |       |       |        |

| P4        | 0     |       | 1      | <b>P9</b>  |       |       |        |

| P5        | 0     |       | 1      | P10        |       |       |        |

| 1 | ld   | X6,0(X10) | R | - 1 | AR  | AC  |

|---|------|-----------|---|-----|-----|-----|

| 2 | add  | X7,X6,X12 | R | - 1 | 1   | - 1 |

| 3 | sd   | X7,0(X10) |   | R   | - 1 | - 1 |

| 4 | addi | X10,X10,8 |   | R   | 1.0 | IN  |

- 5 bne X10,X5,L00P

- © ld X6,0(X10)

- add X7, X6, X12

- 8 sd X7,0(X10)

- 9 addi X10,X10,8

- 10 bne X10, X5, LOOP

|    | Ren        | amed instru | ction      |

|----|------------|-------------|------------|

| 1  | <b>1</b> d | P1, 0(X16   | 9)         |

| 2  | add        | P2, P1, )   | <b>(12</b> |

| 3  | sd         | P2, 0(X16   | 9)         |

| 4  | addi       | P3, X10,    | 8          |

| 5  | bne        | P3, X5, I   | -00P       |

| 6  | <b>1</b> d | P4, 0(P3)   |            |

| 7  | add        | P5, P1, )   | <b>(12</b> |

| 8  | sd         | P5, 0(P3)   |            |

| 9  | addi       | P6, P3, 8   | 3          |

| 10 | bne        | P6, 0(X16   | 9)         |

| - 1 | AR | AQ  | MEM | WB  |

|-----|----|-----|-----|-----|

| 1   | 1  | 11  | - 1 | 1.0 |

| R   | ı  | - 1 | ı   | 1   |

| R   | 1  | INT | WB  |     |

|     | R  | - 1 | I   | BR  |

|     | R  | - 1 | ı   | AR  |

|     |    | R   | - 1 | - 1 |

|     |    | R   | - 1 | I   |

|     |    |     | R   | I   |

|     |    |     | R   | I   |

|     |    |     |     |     |

|            | Physical Register |

|------------|-------------------|

| <b>X</b> 5 |                   |

| <b>X</b> 6 | P1                |

| <b>X7</b>  | P5                |

| X10        | Р3                |

| X12        |                   |

|           | Valid | Value I | n use |            | Valid | Value | In use |

|-----------|-------|---------|-------|------------|-------|-------|--------|

| P1        | 1     |         | 1     | P6         |       |       |        |

| P2        | 0     |         | 1     | <b>P</b> 7 |       |       |        |

| <b>P3</b> | 1     |         | 1     | P8         |       |       |        |

| P4        | 0     |         | 1     | <b>P</b> 9 |       |       |        |

| P5        | 0     |         | 1     | P10        |       |       |        |

| 1 | ld   | X6,0(X10) | R |

|---|------|-----------|---|

| 2 | add  | X7,X6,X12 | R |

| 3 | sd   | X7,0(X10) |   |

| 4 | addi | X10,X10,8 |   |

- 5 bne X10,X5,L00P

- © ld X6,0(X10)

- ② add X7,X6,X12

- ® sd X7,0(X10)

- addi X10,X10,8

- 10 bne X10, X5, LOOP

|     | Ren           | amed i | nstruction        |

|-----|---------------|--------|-------------------|

| 1 - | <del>ld</del> |        | <del>9(X10)</del> |

| 2   | add           | P2, I  | P1, X12           |

| 3   | sd            | P2, (  | 9(X10)            |

| 4   | addi          | P3, 2  | X10, 8            |

| 5   | bne           | P3, 2  | X5, LOOP          |

| 6   | <b>1</b> d    | P4, (  | 9(P3)             |

| 7   | add           | P5, I  | P1, X12           |

| 8   | sd            | P5, (  | 9(P3)             |

| 9   | addi          | P6, I  | P3, 8             |

| 10  | bne           | P6, (  | 9(X10)            |

| MEM | WB             |                          |

|-----|----------------|--------------------------|

| 1   | - 1            | INT                      |

|     | ı              | - 1                      |

| WB  |                |                          |

| 1   | BR             | WB                       |

|     | AR             | AQ                       |

| 1   | ı              | 1                        |

| 1   | ı              | 1                        |

| R   | ı              | 1                        |

| R   | ı              | 1                        |

|     | I I WB I I I R | I I WB I BR I AR I I R I |

| Physical Register |    |  |  |  |  |  |

|-------------------|----|--|--|--|--|--|

| <b>X</b> 5        |    |  |  |  |  |  |

| <b>X6</b>         | P1 |  |  |  |  |  |

| <b>X7</b>         | P5 |  |  |  |  |  |

| X10               | Р3 |  |  |  |  |  |

| X12               |    |  |  |  |  |  |

|           | Valid | Value In u | se  | Valid | Value | In use |

|-----------|-------|------------|-----|-------|-------|--------|

| P1        | 1     | 1          | P6  |       |       |        |

| P2        | 0     | 1          | P7  |       |       |        |

| <b>P3</b> | 1     | 1          | P8  |       |       |        |

| P4        | 0     | 1          | P9  |       |       |        |

| P5        | 0     | 1          | P10 |       |       |        |

| 1 | ld   | X6,0(X10)   | R | - 1 |

|---|------|-------------|---|-----|

| 2 | add  | X7,X6,X12   | R | - 1 |

| 3 | sd   | X7,0(X10)   |   | R   |

| 4 | addi | X10,X10,8   |   | R   |

| 5 | bne  | X10,X5,LOOP |   |     |

- © ld X6,0(X10)

- ② add X7,X6,X12

- sd X7,0(X10)

- 9 addi X10,X10,8

- 10 bne X10, X5, LOOP

| Renamed instruction |               |              |  |  |  |  |

|---------------------|---------------|--------------|--|--|--|--|

| 1 -                 | <del>ld</del> | P1, 0(X10)   |  |  |  |  |

| 2                   | add           | P2, P1, X12  |  |  |  |  |

| 3                   | sd            | P2, 0(X10)   |  |  |  |  |

| 4                   | addi          | P3, X10, 8   |  |  |  |  |

| 5 -                 | bne           | P3, X5, LOOP |  |  |  |  |

| 6                   | <b>1</b> d    | P4, 0(P3)    |  |  |  |  |

| 7                   | add           | P5, P1, X12  |  |  |  |  |

| 8                   | sd            | P5, 0(P3)    |  |  |  |  |