# When sequential circuits meet datapath components (3)

Prof. Usagi

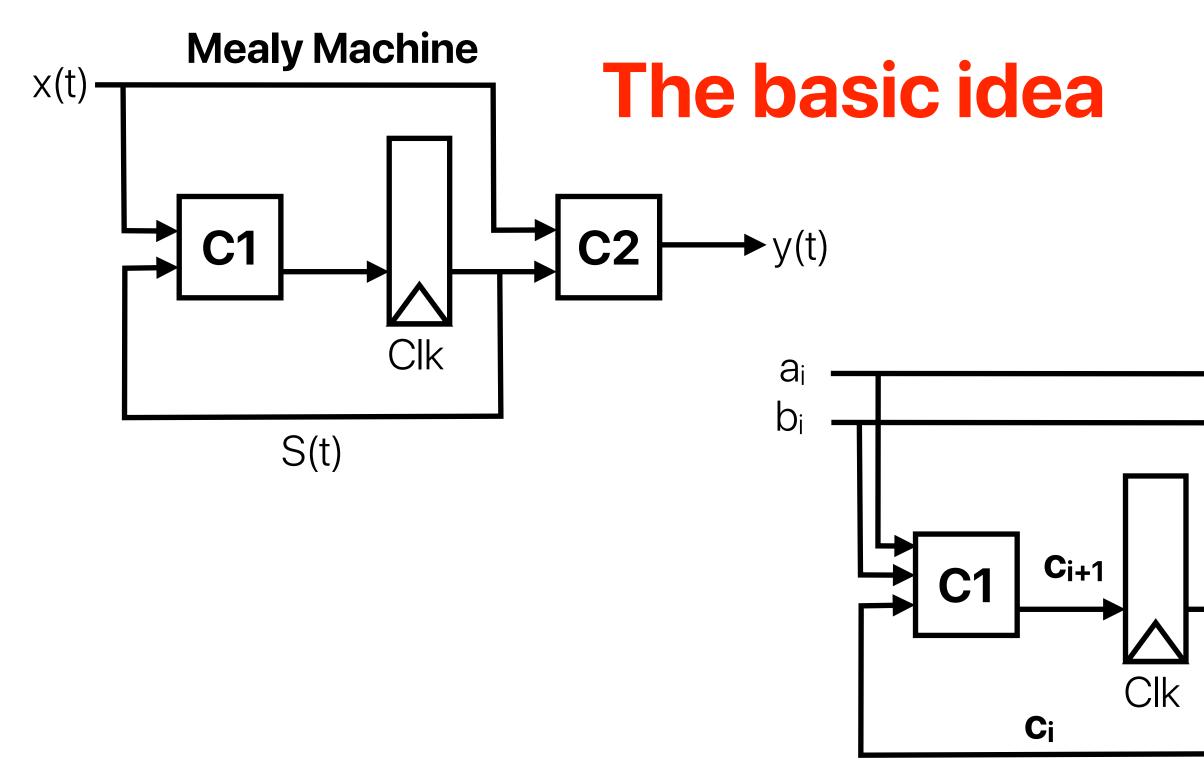

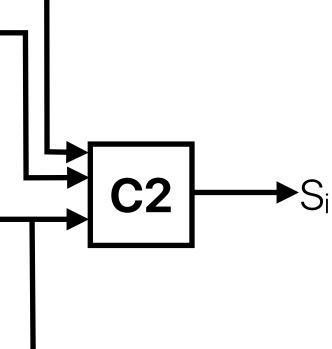

# **Serial Adder**

Feed  $a_i$  and  $b_i$  and generate  $s_i$  at time i. Where is  $c_i$  and  $c_{i+1}$ ?

#### **Excitation Table of Serial Adder**

| ai | bi | Ci | Ci+1 | Si |

|----|----|----|------|----|

| 0  | 0  | 0  | 0    | 0  |

| 0  | 0  | 1  | 0    | 1  |

| 0  | 1  | 0  | 0    | 1  |

| 0  | 1  | 1  | 1    | 0  |

| 1  | 0  | 0  | 0    | 1  |

| 1  | 0  | 1  | 1    | 0  |

| 1  | 1  | 0  | 1    | 0  |

| 1  | 1  | 1  | 1    | 1  |

#### **Excitation Table of Serial Adder**

| ai | bi | Ci | Ci+1 | Si |

|----|----|----|------|----|

| 0  | 0  | 0  | 0    | 0  |

| 0  | 0  | 1  | 0    | 1  |

| 0  | 1  | 0  | 0    | 1  |

| 0  | 1  | 1  | 1    | 0  |

| 1  | 0  | 0  | 0    | 1  |

| 1  | 0  | 1  | 1    | 0  |

| 1  | 1  | 0  | 1    | 0  |

| 1  | 1  | 1  | 1    | 1  |

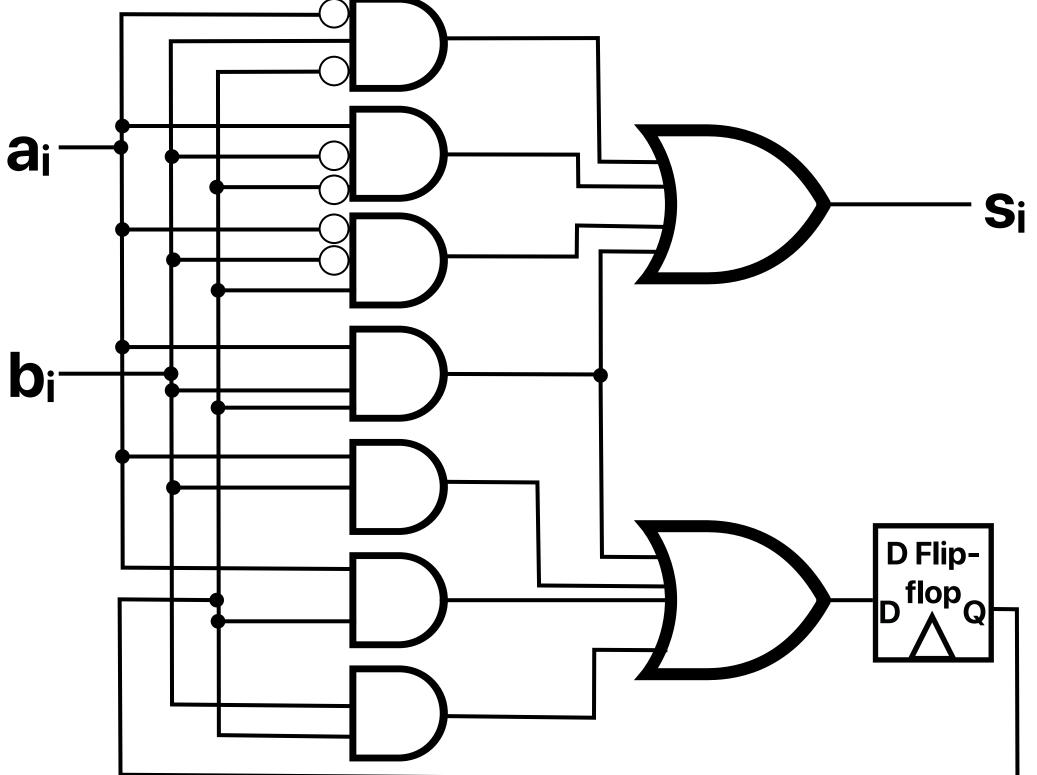

### **Pipelining**

- Different parts of the hardware works on different requests/ commands simultaneously

- A clock signal controls and synchronize the beginning and the end of each part/stage of the work

- A pipeline register between different parts of the hardware to keep intermediate results necessary for the upcoming work

- Register is basically an array of flip-flops!

#### Pipelining

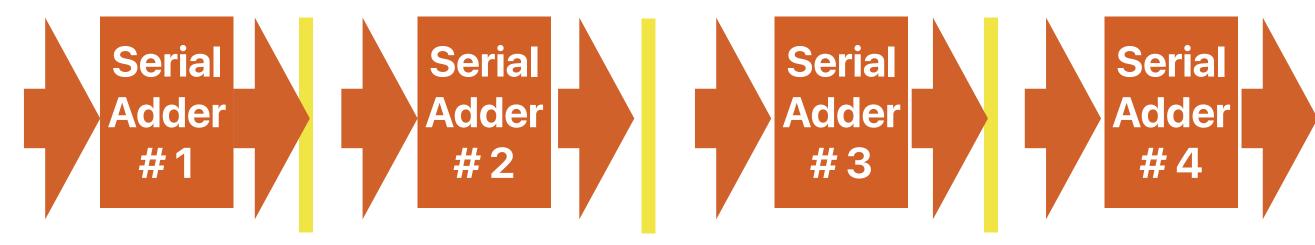

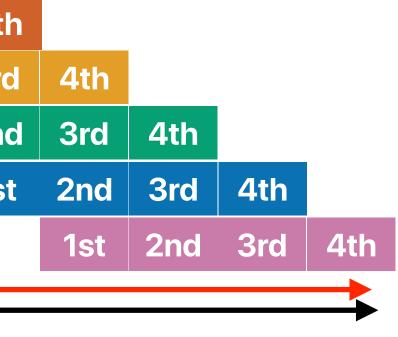

#### **Pipelining a 4-bit serial adder**

### Pipelining a 4-bit serial adder

add a, b add c, d add e, f add g, h add i, j add k, 1 add m, n add **o**, p add q, r add s, t add u, v

|     |     |     |     |                           |            |     |       | C   | 10          |  |

|-----|-----|-----|-----|---------------------------|------------|-----|-------|-----|-------------|--|

| 1st | 2nd | 3rd | 4th |                           |            |     |       | Cyc |             |  |

|     | 1st | 2nd | 3rd | 4th                       |            |     |       | Δ   | dd          |  |

|     |     | 1st | 2nd | 3rd                       | 4th        |     |       | 110 | <i>iU</i>   |  |

|     |     |     | 1st | 2nd                       | <b>3rd</b> | 4th |       |     |             |  |

|     |     |     |     | 1st                       | 2nd        | 3rd | 4th   |     |             |  |

|     |     |     |     |                           | 1st        | 2nd | 3rd   | 4th |             |  |

|     |     |     |     |                           |            | 1st | 2nd   | 3rd | 4t          |  |

|     |     |     |     |                           |            |     | 1st   | 2nd | 3rc         |  |

|     |     |     |     |                           | er thi     | -   | _     | 1st | 2nd         |  |

|     |     |     |     |                           |            |     | letin |     | <b>1</b> st |  |

|     |     |     |     | add operation each cycle! |            |     |       |     |             |  |

t

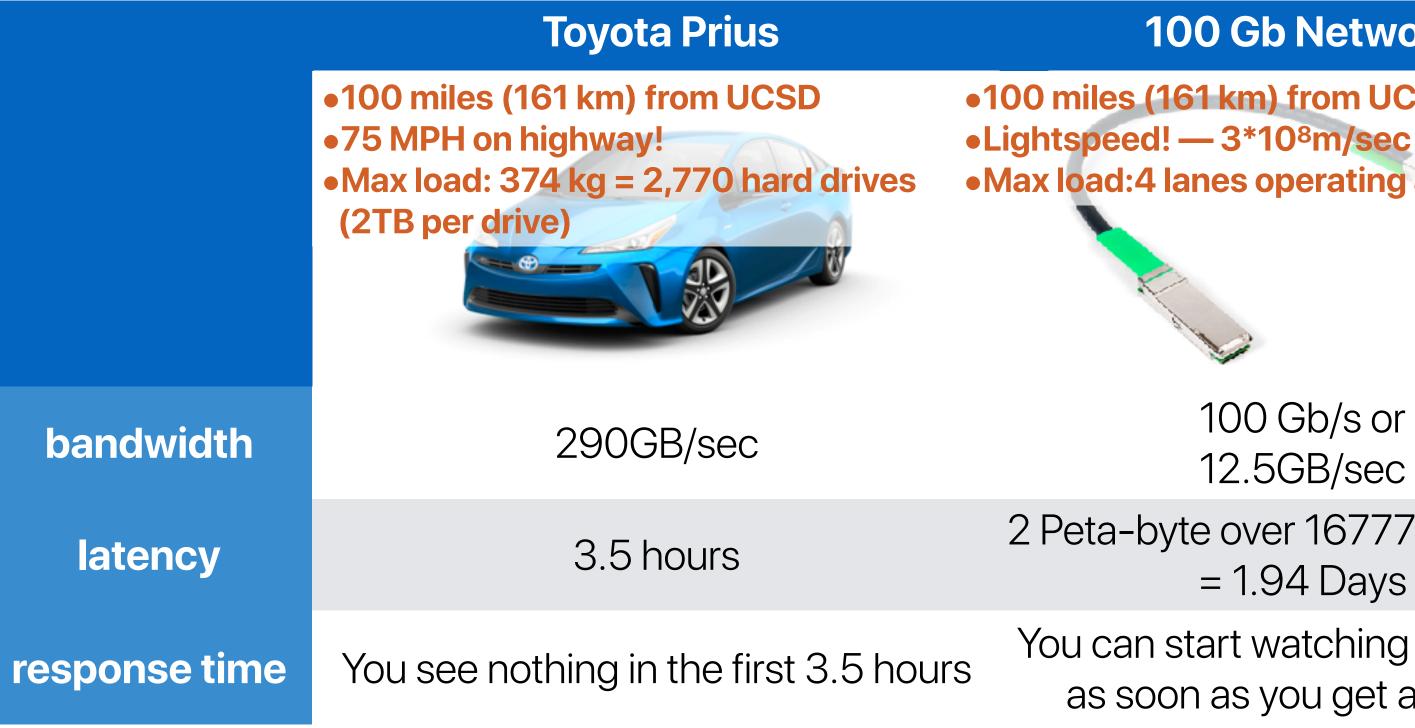

### Latency/Delay v.s. Bandwidth/Throughput

- Latency the amount of time to finish an operation

- access time

- response time

- Throughput the amount of work can be done within a given period of time

- bandwidth (MB/Sec, GB/Sec, Mbps, Gbps)

- IOPs

- MFLOPs

### Latency/Delay v.s. Throughput

#### **100 Gb Network**

#### 100 miles (161 km) from UCSD •Max load:4 lanes operating at 25GHz

#### 100 Gb/s or 12.5GB/sec

#### 2 Peta-byte over 167772 seconds = 1.94 Days

You can start watching the movie as soon as you get a frame!

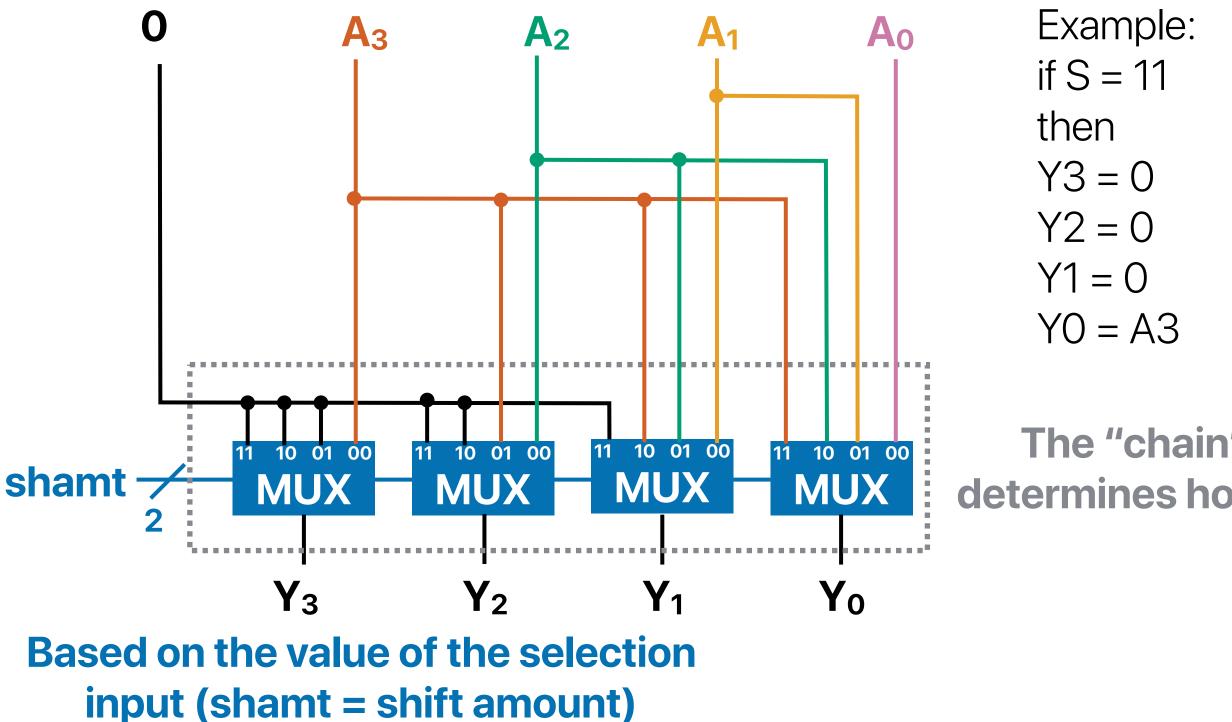

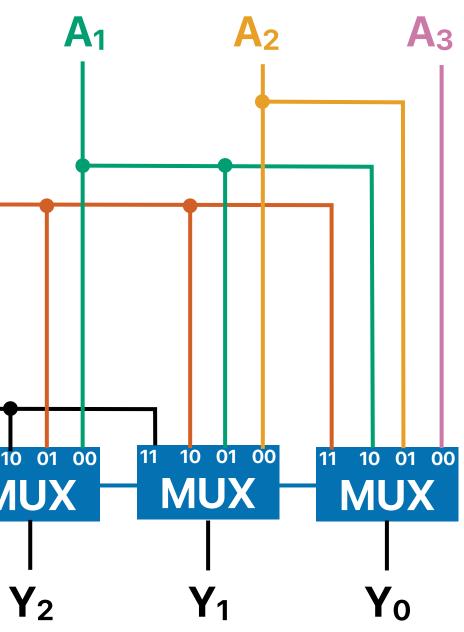

### **Recap: Shift "Right"**

Example: Example: if S = 10if S = 01then then Y3 = 0Y3 = 0Y2 = 0 Y2 = A3Y1 = A3 Y1 = A2YO = A2 YO = A1

The "chain" of multiplexers determines how many bits to shift

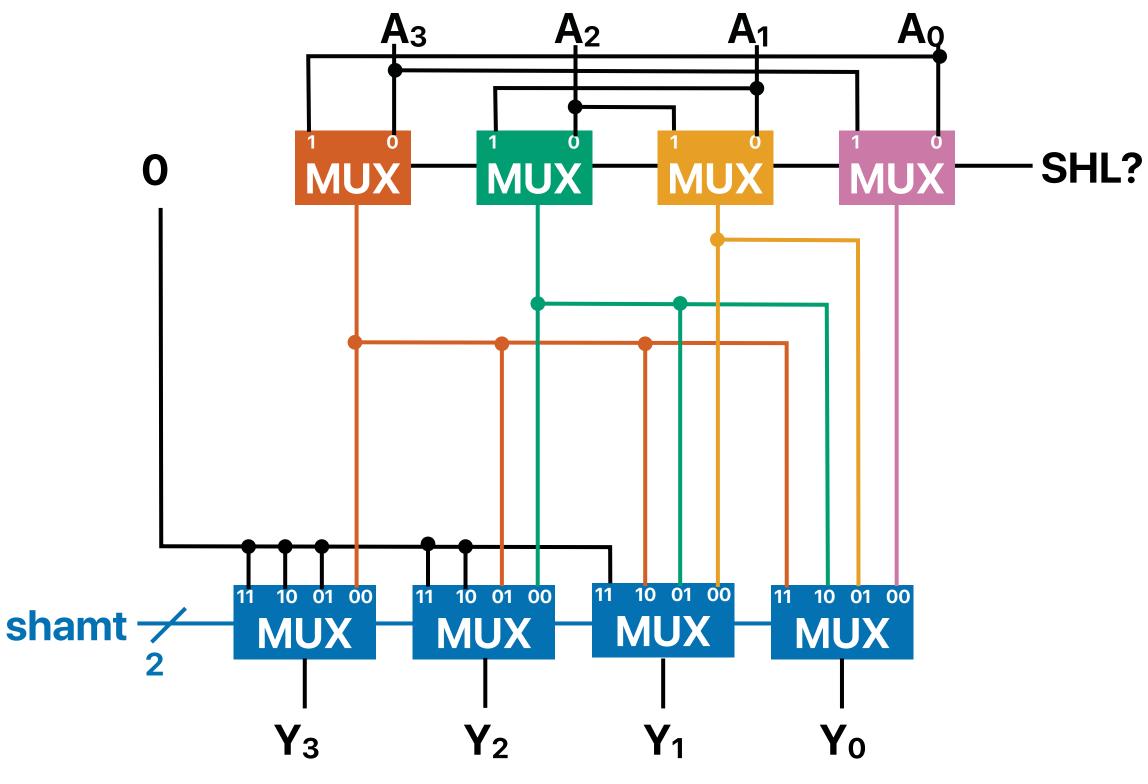

# Shifters

#### Shift "Left"

| Example:<br>if S = 01 | Example:<br>if S = 10 | Example:<br>if S = 11 | 0       | Ao                    |

|-----------------------|-----------------------|-----------------------|---------|-----------------------|

| then<br>Y3 = A2       | then<br>Y3 = A1       | then                  |         |                       |

| Y2 = A1               | Y2 = A0               | Y3 = A0<br>Y2 = 0     |         |                       |

| Y1 = A0 $Y0 = 0$      | Y1 = 0 $Y0 = 0$       | Y1 = 0 $Y0 = 0$       |         |                       |

|                       |                       |                       |         |                       |

|                       |                       |                       | shamt - | 11 10 01 00 11 10     |

|                       |                       |                       | 2       |                       |

|                       |                       |                       |         | <b>Y</b> <sub>3</sub> |

#### **Generic Shifter**

# Multiplier

### **Binary multiplication**

Thinking about how you do this by hand in decimal!

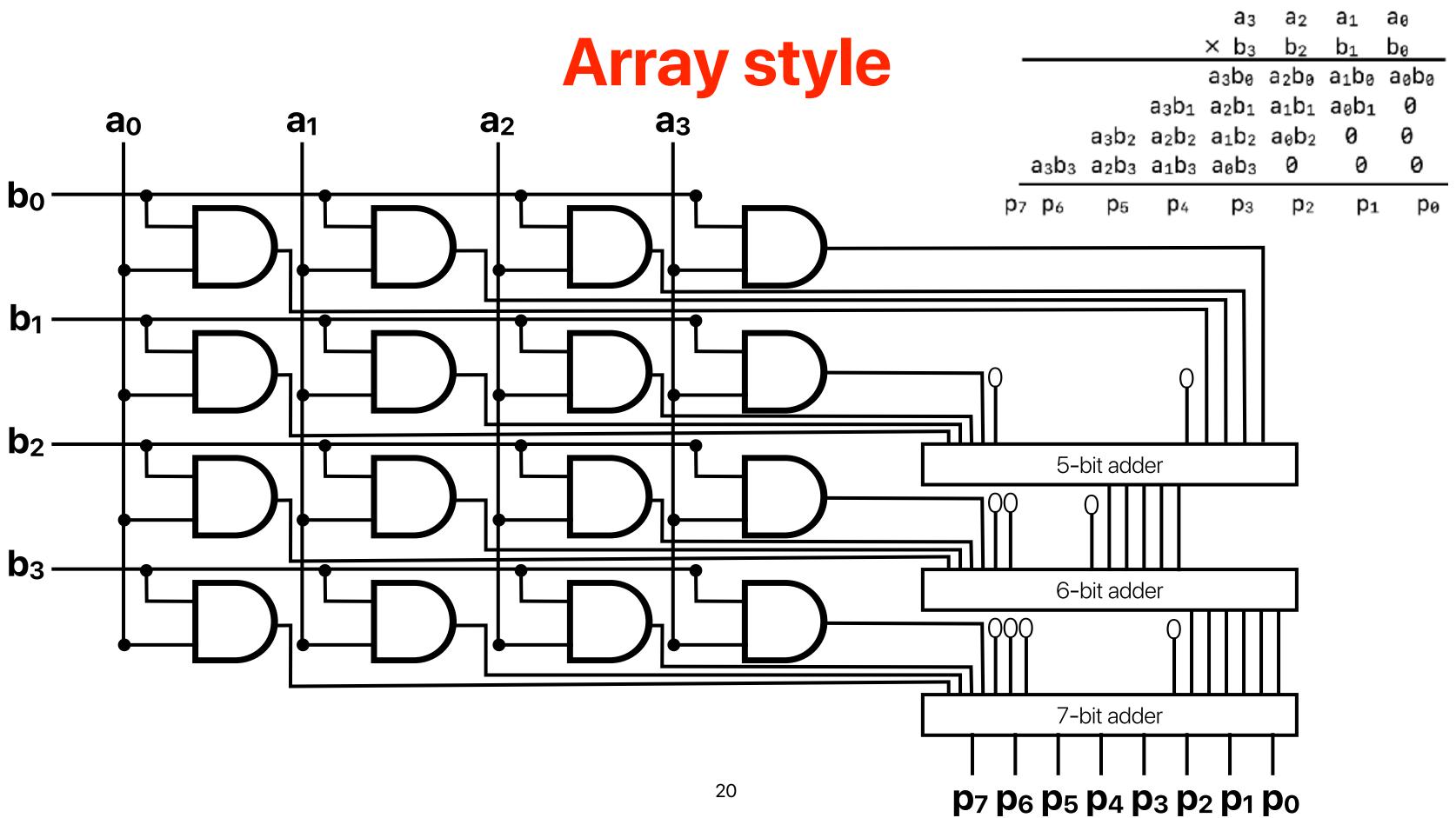

|   |   |   | 1 | 2 | 3 | 4 |   |   |   | 0 | 1 | 1 | 1 |                |                               |            |                               | <b>a</b> <sub>3</sub>         | <b>a</b> <sub>2</sub>         | aı                            | ao                            |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|----------------|-------------------------------|------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|

|   |   | Х | 5 | 6 | 7 | 8 |   |   | Х | 1 | 1 | 0 | 0 |                |                               |            |                               | $\times b_3$                  | $b_2$                         | b <sub>1</sub>                | b <sub>0</sub>                |

|   |   |   | 9 | 8 | 7 | 2 |   |   |   | 0 | 0 | 0 | 0 | pp1            |                               |            |                               | a <sub>3</sub> b <sub>0</sub> | $a_2b_0$                      | a <sub>1</sub> b <sub>0</sub> | a <sub>0</sub> b <sub>0</sub> |

|   |   | 8 | 6 | 3 | 8 |   |   |   | 0 | 0 | 0 | 0 |   | pp2            |                               |            | a <sub>3</sub> b <sub>1</sub> | $a_2b_1$                      | $a_1b_1$                      | a <sub>0</sub> b <sub>1</sub> | 0                             |

|   | 7 | 4 | 0 | 4 |   |   |   | 0 | 1 | 1 | 1 |   |   | ррЗ            |                               | $a_3b_2$   | $a_2b_2$                      | $a_1b_2$                      | a <sub>0</sub> b <sub>2</sub> | 0                             | 0                             |

| 6 | 1 | 7 | 0 |   |   |   | 0 | 1 | 1 | 1 |   |   |   | pp4            | a <sub>3</sub> b <sub>3</sub> | $a_2b_3$   | $a_1b_3$                      | a <sub>0</sub> b <sub>3</sub> | 0                             | 0                             | 0                             |

| 7 | 0 | 0 | 6 | 6 | 5 | 2 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | р <sub>7</sub> | <b>p</b> 6                    | <b>p</b> 5 | <b>p</b> 4                    | p <sub>3</sub>                | p <sub>2</sub>                | p <sub>1</sub>                | p <sub>0</sub>                |

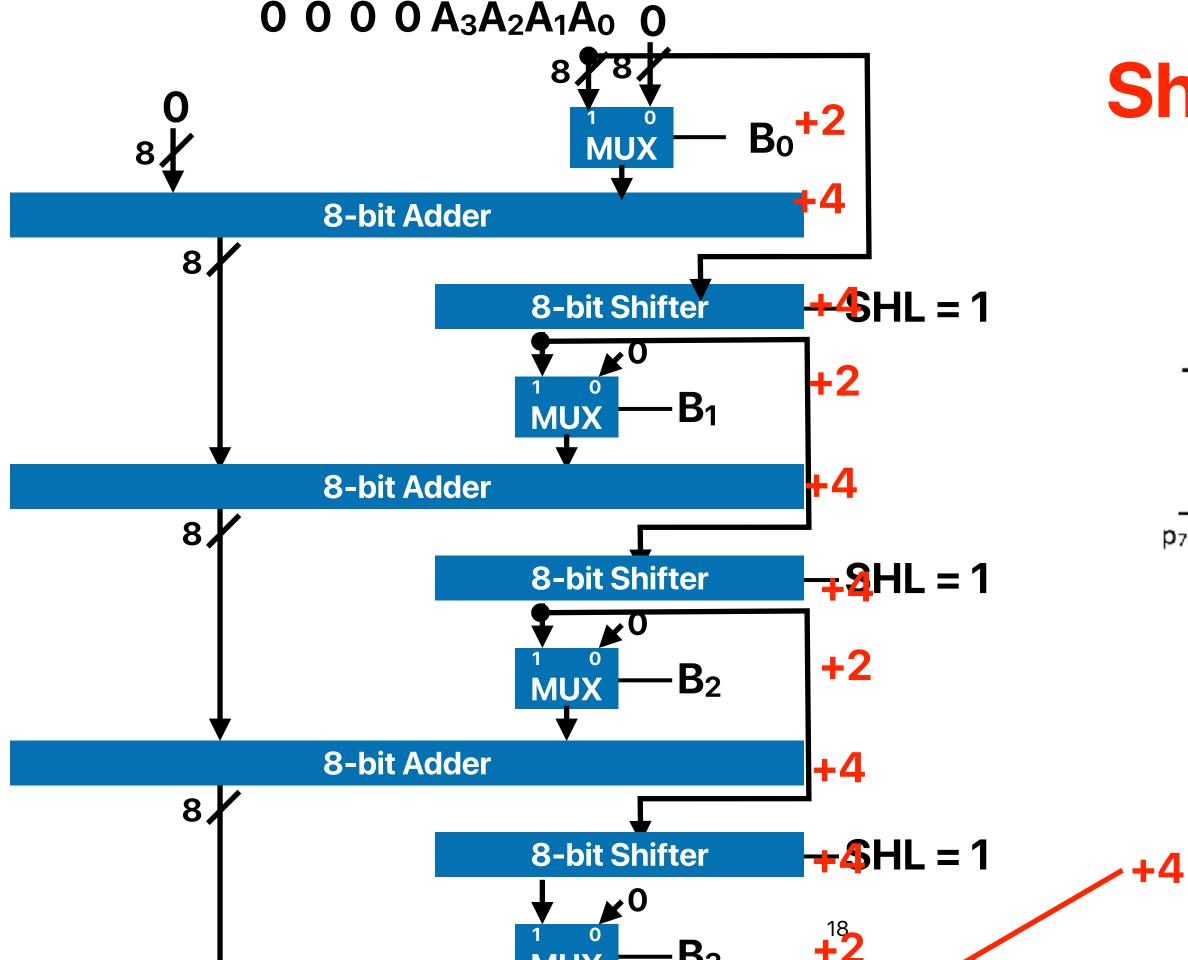

#### Shift and add

|              |                |            | a3           | a2    | $a_1$ | aø   |

|--------------|----------------|------------|--------------|-------|-------|------|

|              |                |            | $\times b_3$ | $b_2$ | bı    | be   |

|              |                |            | a₃b₀         | a₂b₀  | a₁b₀  | a₀b₀ |

|              |                | a₃bı       | $a_2b_1$     | a₁b₁  | a₀bı  | 0    |

|              | a₃b₂           | $a_2b_2$   | a1b2         | a₀b₂  | 0     | 0    |

| $a_3b_3$     | a2b3           | a₁b₃       | a₀b₃         | 0     | 0     | 0    |

| 7 <b>p</b> 6 | p <sub>5</sub> | <b>p</b> 4 | p₃           | $p_2$ | p1    | p0   |

#### - 36 gate delays

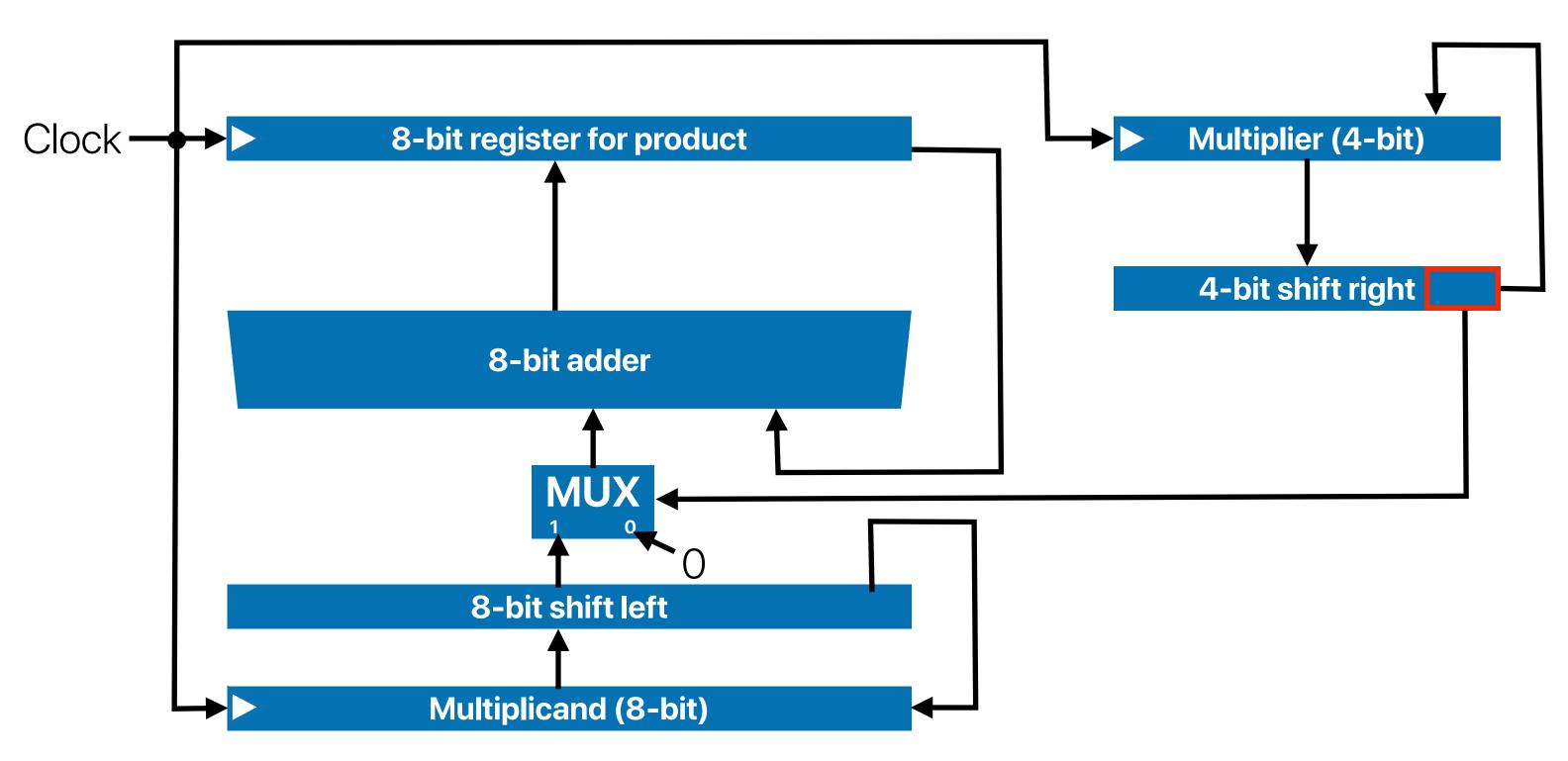

#### 4-bit serial shift-and-add multiplier

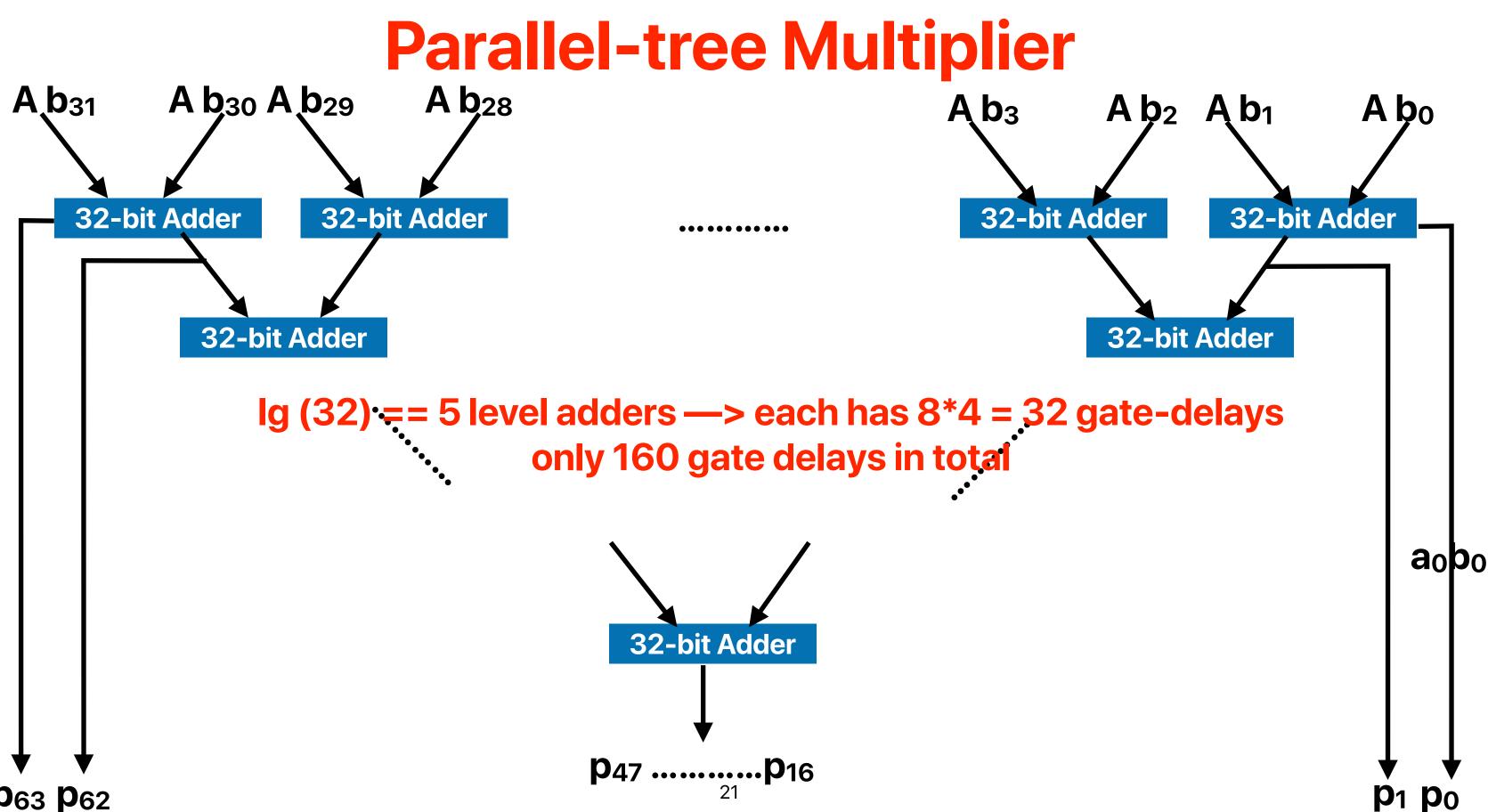

**p**<sub>63</sub> **p**<sub>62</sub>

# Divider

### **Division of positive binary numbers**

- Repeated subtraction

- Set quotient to 0

- Repeat while (dividend >= divisor)

- Subtract divisor from dividend

- Add 1 to quotient

- When dividend < divisor:

- Reminder = dividend

- Quotient is correct

# Put everything all together! ALU — arithmetic logic unit

#### Announcement

- Assignment 2 due TONIGHT

- All challenge questions up to **3.5**

- Reading quiz 5 due 4/28 **BEFORE** the lecture

- Under iLearn > reading quizzes

- Lab 3 due 4/30

- Watch the video and read the instruction BEFORE your session

- There are links on both course webpage and iLearn lab section

- Submit through iLearn > Labs

- Midterm on 5/7 during the lecture time, access through iLearn no late submission is allowed — make sure you will be able to take that at the time

- Check your grades in iLearn

### Electrical Computer Science Engineering