# **Sequential Circuits**

Prof. Usagi

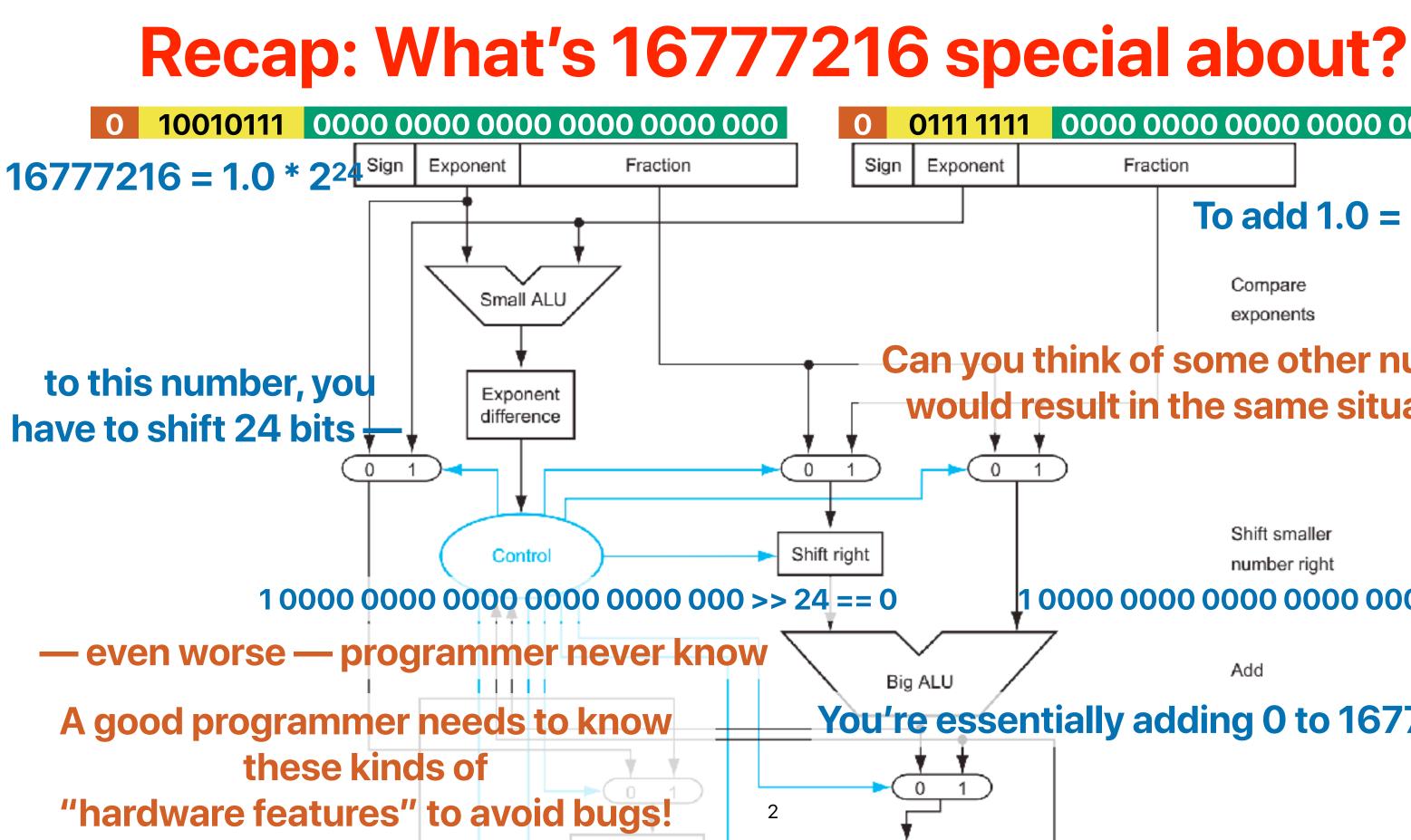

### 0000 0000 0000 0000 0000 0000

Fraction

### To add $1.0 = 1.0 * 2^{\circ}$

Compare

exponents

### **Can you think of some other numbers** would result in the same situation?

Shift smaller number right 0000 0000 0000 0000 0000 000

Add

### You're essentially adding 0 to 16777216

# **Recap: Other floating point formats**

| <b>16-bit half</b> | +/- | Exp (5-bit) Fracti | on (10-bit) added i |

|--------------------|-----|--------------------|---------------------|

| 32-bit float       | +/- | Exponent (8-bit)   | Fraction (23-       |

| 64-bit double      | +/- | Exponent (11-bit)  | Fractio             |

- Not all applications require "high precision"

- Deep neural networks are surprisingly error tolerable

- Again Trade-off between area-efficiency/cost/performance/ accuracy

### in 2008

- -bit)

- ion (52-bit)

# **Recap: Combinational v.s. sequential logic**

- Combinational logic

- The output is a pure function of its current inputs

- The output doesn't change regardless how many times the logic is triggered — Idempotent

- Sequential logic

- The output depends on current inputs, previous inputs, their history

### **Sequential circuit has memory!**

# **Recap: Theory behind each**

- A Combinational logic is the implementation of a **Boolean Algebra** function with only Boolean Variables as their inputs

- A Sequential logic is the implementation of a **Finite-State Machine**

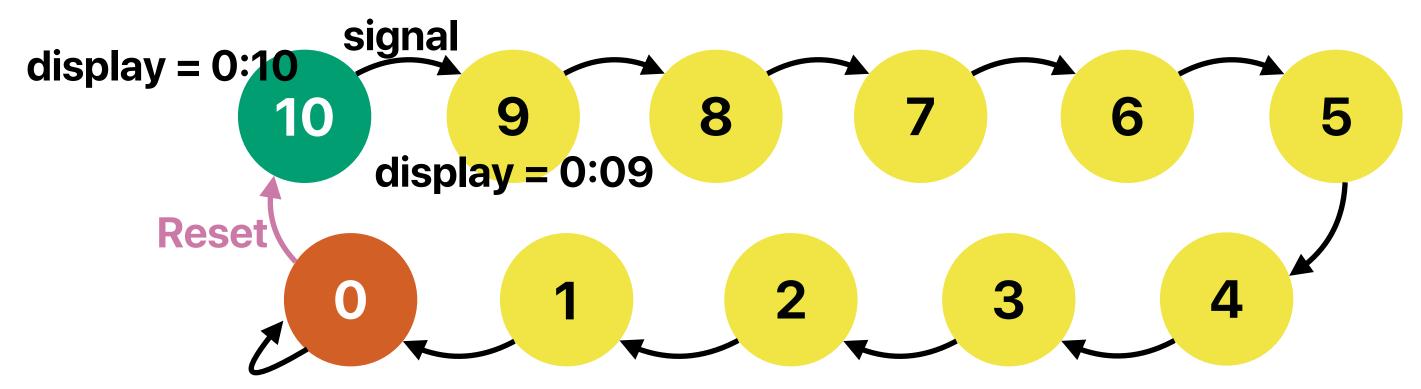

# :10

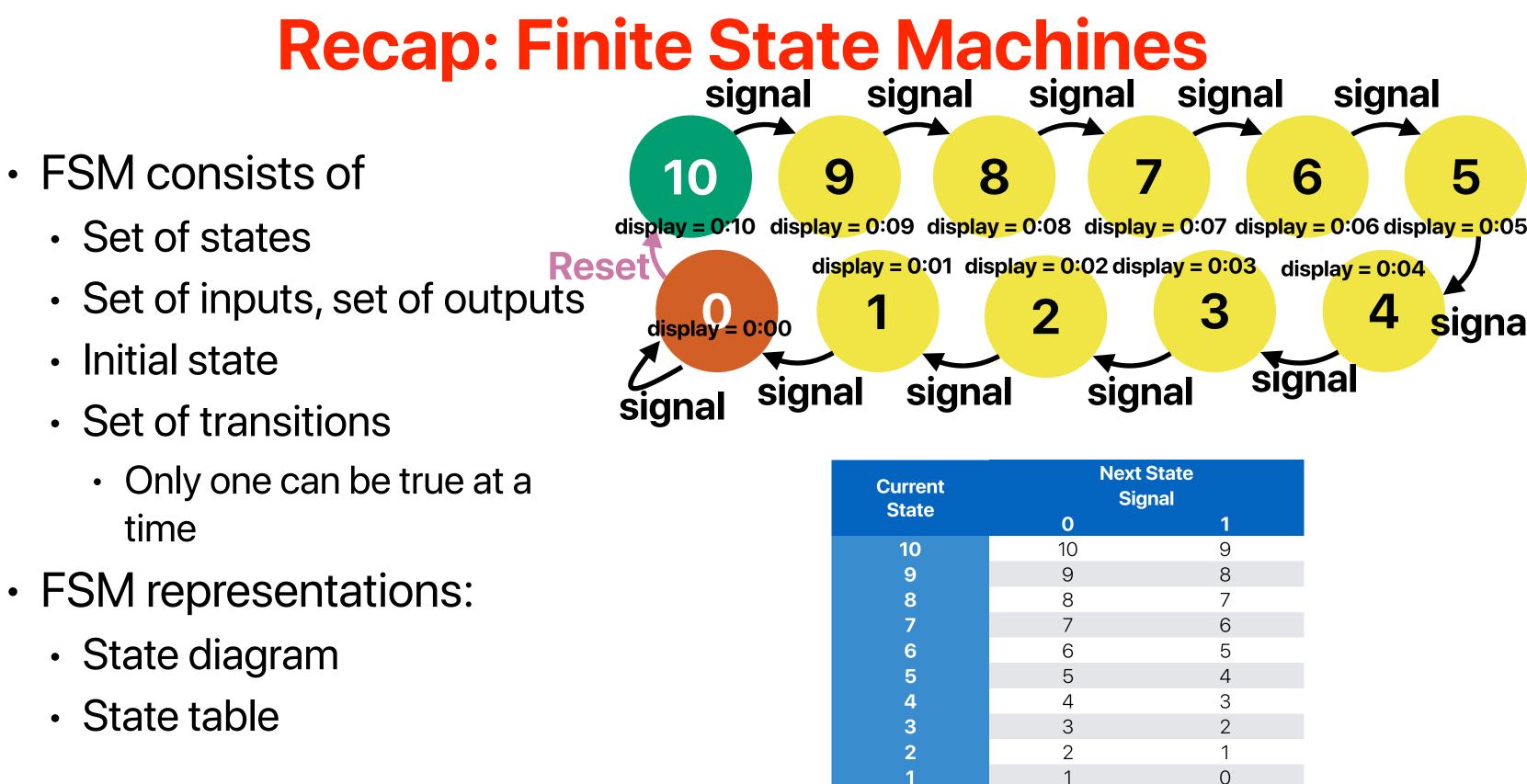

# **Recap: Count-down Timer**

- What do we need to implement this timer?

- Set an initial value/"state" of the timer

- "Signal" the design every second

- The design changes its "state" every time we received the signal until we reaches "0" — the final state

|                       | Next State<br>Signal |        |  |

|-----------------------|----------------------|--------|--|

| 0                     |                      | 1      |  |

| 10                    |                      | 9<br>8 |  |

| 9                     |                      |        |  |

| 9<br>8<br>7           |                      | 7      |  |

|                       |                      | 6      |  |

| 6                     |                      | 5      |  |

| 5                     |                      | 4      |  |

| 4                     |                      | 4<br>3 |  |

| 6<br>5<br>4<br>3<br>2 |                      | 2      |  |

| 2                     |                      | 1      |  |

| 1                     |                      | 0      |  |

| 0                     |                      | 0      |  |

# **Recap: Life on Mars**

- Mars rover has a binary input x. When it receives the input sequence x(t-2, t) = 001 from its life detection sensors, it means that the it has detected life on Mars and the output y(t)= 1, otherwise y(t) = 0 (no life on Mars).

- This pattern recognizer should have

- A. One state because it has one output

- B. One state because it has one input

- C. Two states because the input can be 0 or 1

- D. More than two states because ....

- E. None of the above

- Finite State Machines

- The Basic Form of Memory

- Clock

# Finite-State Machines (cont.)

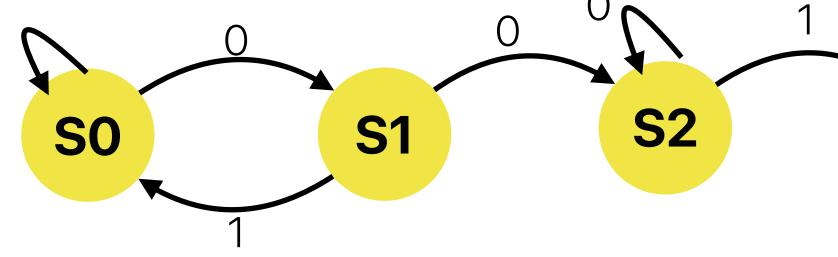

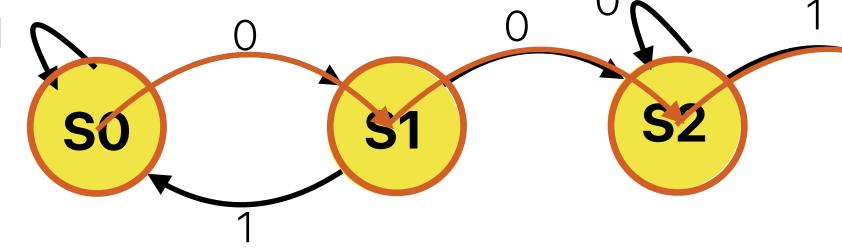

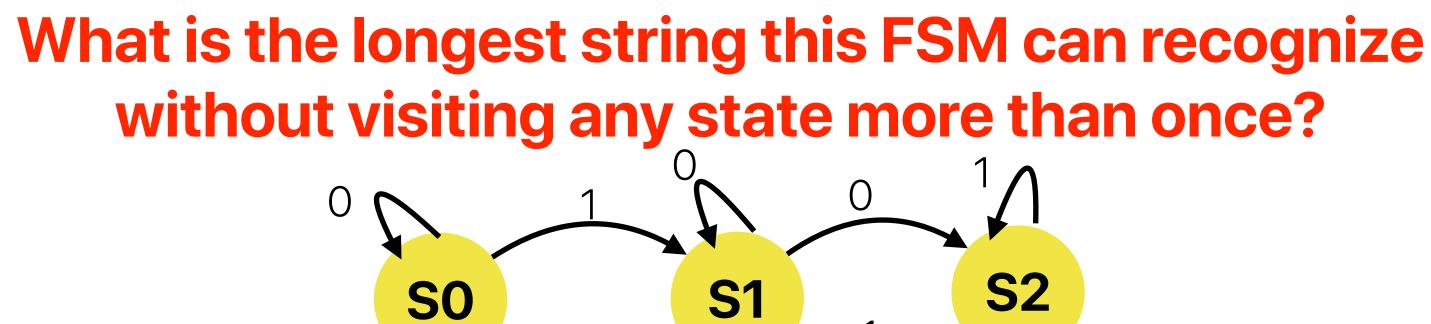

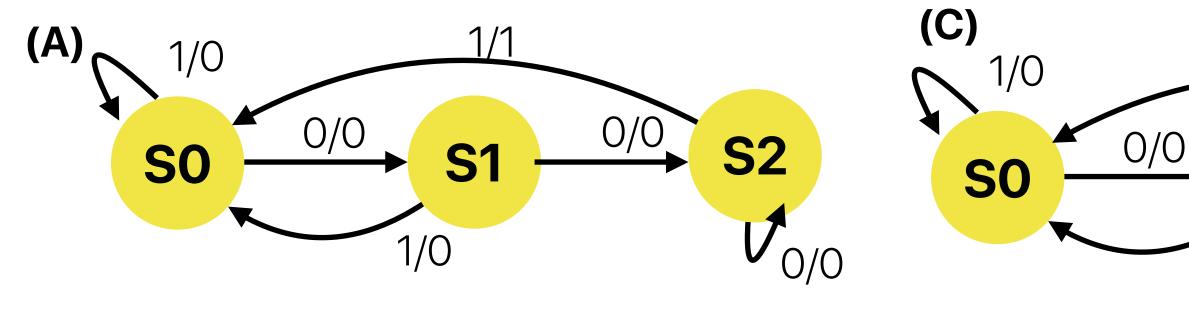

### Poll close in 1:30 What is the longest string this FSM can recognize without visiting any state more than once?

- A. 1

- B. 2

- C. 3

- D. 4

- E. None of the above

# an recognize an once?

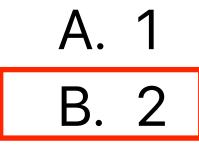

# What is the longest string this FSM can recognize without visiting any state more than once?

- A. 1

- B. 2

- C. 3

- D. 4

- E. None of the above

# an recognize an once?

### Poll close in 1:30 What is the longest string this FSM can recognize without visiting any state more than once?

# $\begin{array}{c} 0 \\ \mathbf{S0} \\ \mathbf{S0} \\ \mathbf{S1} \\ \mathbf{S1} \\ \mathbf{S2} \\ \mathbf{S1} \\ \mathbf{S2} \\ \mathbf{S2} \\ \mathbf{S1} \\ \mathbf{S2} \\ \mathbf{S2} \\ \mathbf{S2} \\ \mathbf{S1} \\ \mathbf{S2} \\ \mathbf{S2} \\ \mathbf{S2} \\ \mathbf{S2} \\ \mathbf{S1} \\ \mathbf{S2} \\ \mathbf{S$

- A. 1

- B. 2

- C. 3

- D. 4

- E. None of the above

- C. 3

- D. 4

- E. None of the above

# Generalization

- Given a string s and a FSM M that accepts/recognize s:

- If  $|\mathbf{s}| > |\mathbf{Q}|$ , then when **M** processes **s**, it must visit one (or more) state(s) more than once

- For a second, let's just consider one state  $(\mathbf{q}_{\mathbf{x}})$  being twice visited

- Let y be the substring of s that is read between the first and second times the twice-visited state  $(\mathbf{q}_{\mathbf{x}})$  is visited

- It must be the case that y could appear repeatedly in s:

- s = [first part of s]y[last part of s] is accepted by the FSM, then also possible inthis FSM:

- [first part of s]yy[last part of s]

- [first part of s]yyyyyyyyyy[last part of s]

- [first part of s][last part of s]

### Introduction to the Theory of COMPUTATION Second Edition

# If you want to learn more ... CS 150

The content of this text differs from the U.S. version

MICHAEL SIPSER

16

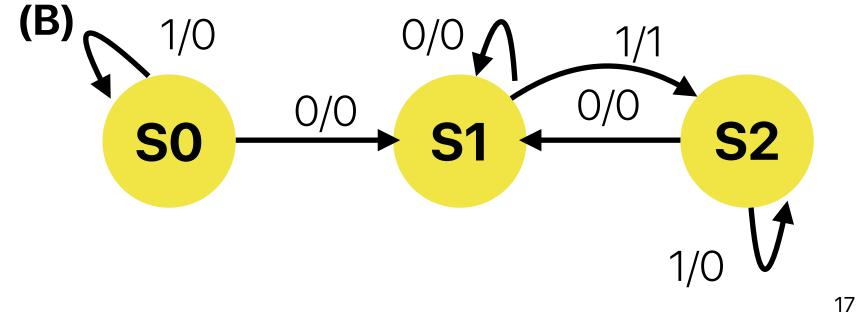

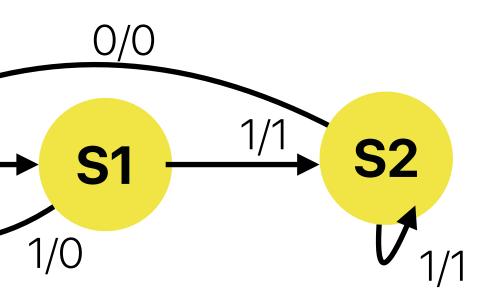

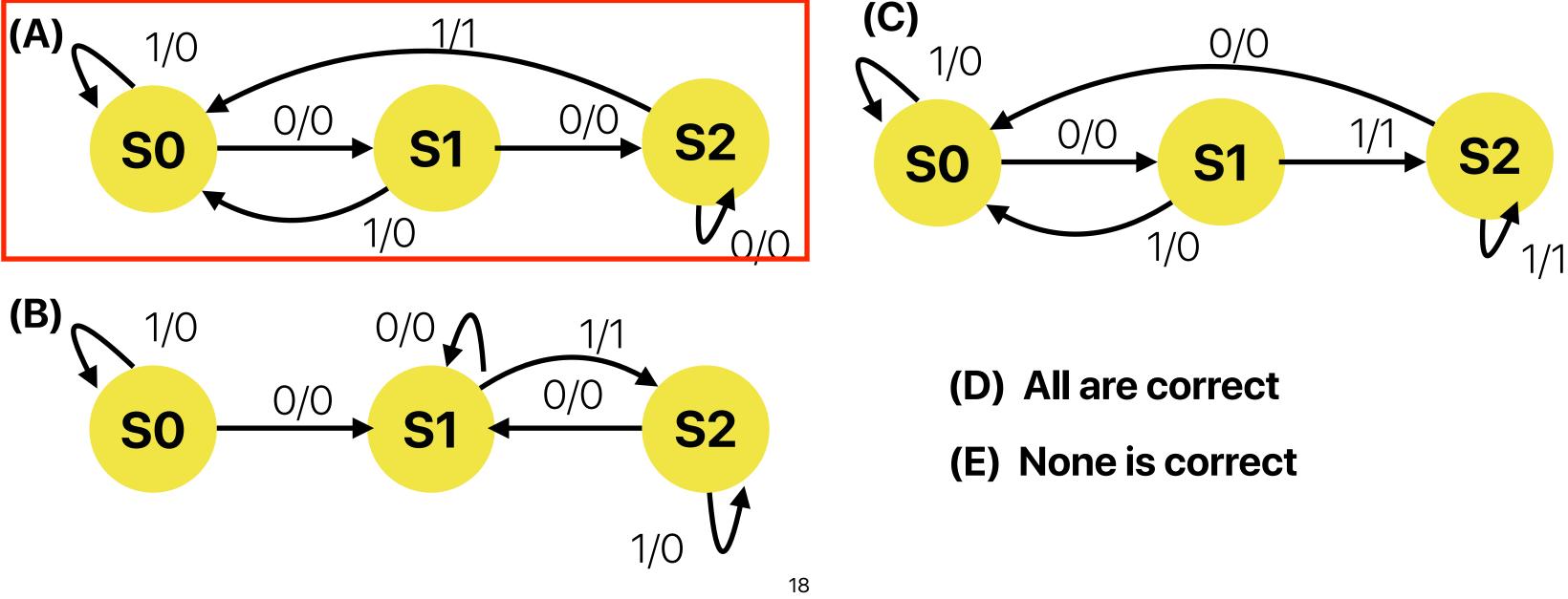

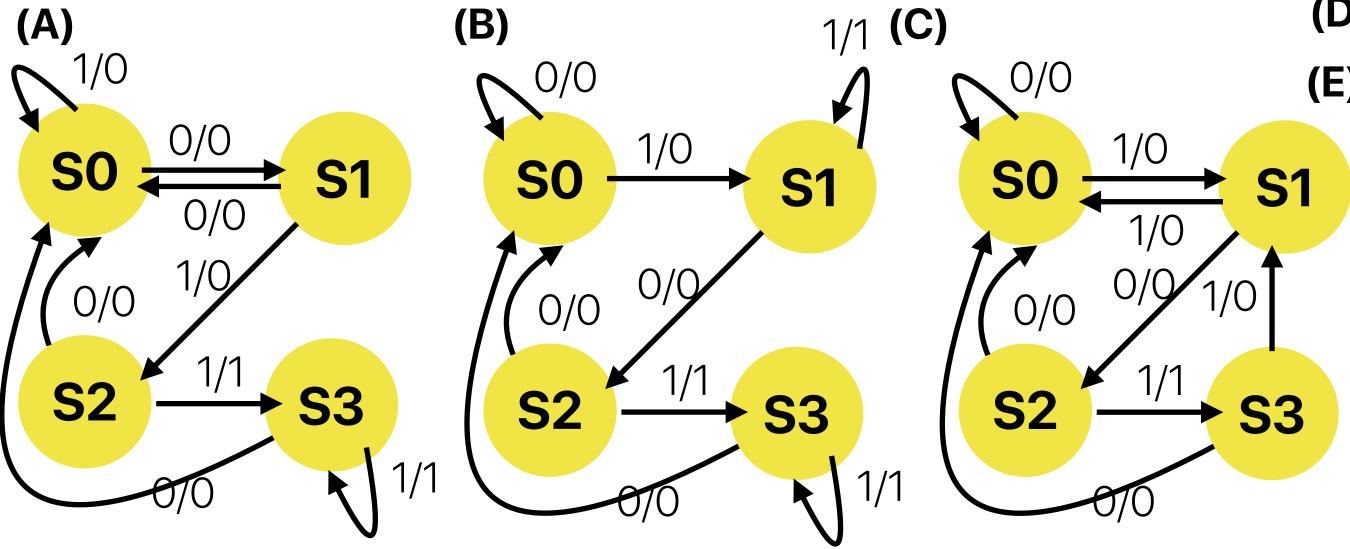

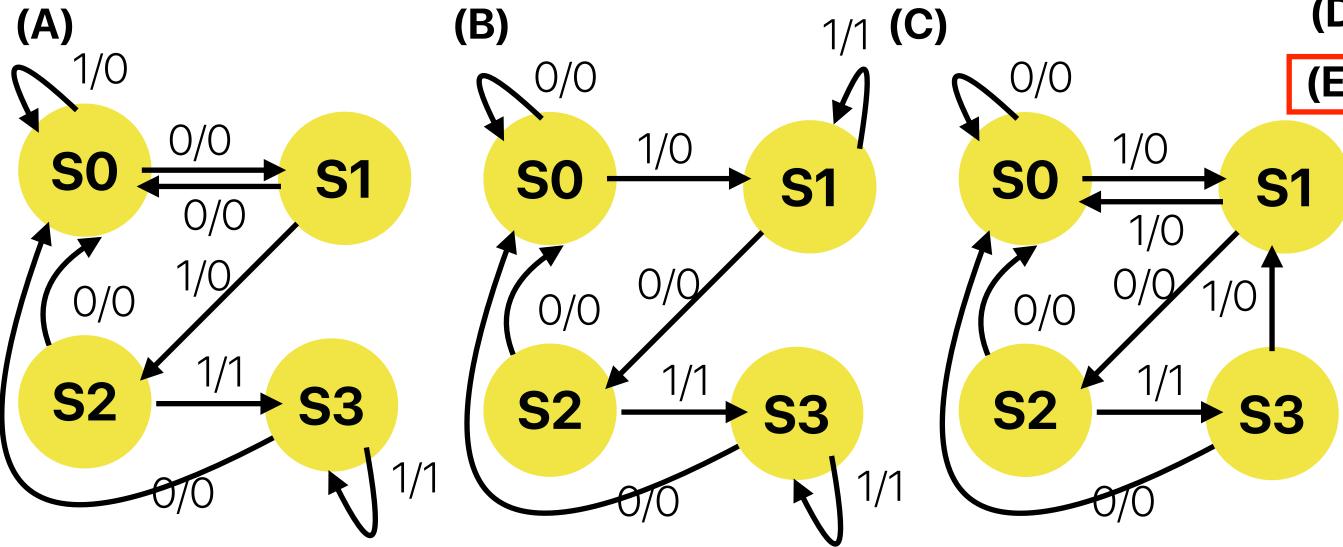

1/0 == Input 1/Output 0

# **FSM for Life on Mars**

Which of the following diagrams is a correct FSM for the 001 pattern recognizer on the Mars rover? (If sees "001", output "1")

**(D)**

### All are correct

(E) None is correct

# **FSM for Life on Mars**

Which of the following diagrams is a correct FSM for the 001 pattern recognizer on the Mars rover? (If sees "001", output "1")

1/0 == Input 1/Output 0

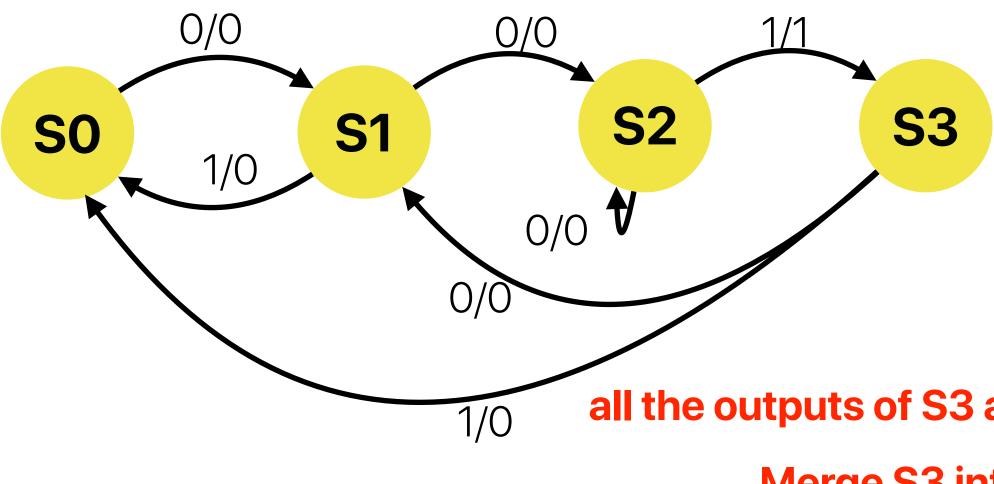

### **FSM for Life on Mars**

### all the outputs of S3 are equal to SO! Merge S3 into S0

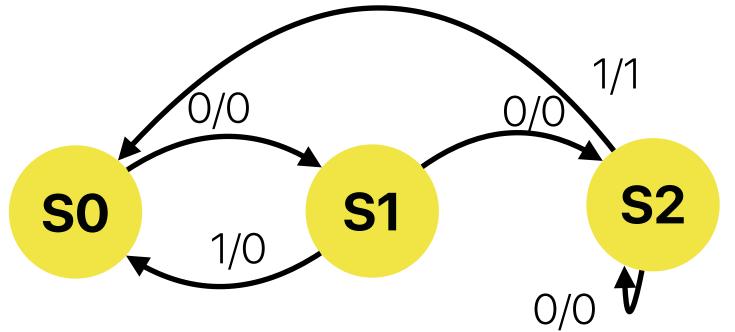

### **FSM for Life on Mars**

### Merge S3 into S0

### **State Transition Table of Life on Mars**

|                     |    | Next State |

|---------------------|----|------------|

| Current<br>State    |    | Input      |

|                     | 0  |            |

| S0 — something else | S1 |            |

| S1—0                | S2 |            |

| S2-00               | S2 |            |

| S3—001              | S1 |            |

- Mars rover has a binary input x. When it receives the input sequence x(t-2, t) = 101 from its life detection sensors, it means that the it has detected life on Mars and the output y(t) = 1, otherwise y(t) = 0 (no life on Mars).

- How many states in the FSM of the pattern recognizer should have

- A. 1

- B. 2

- C. 3

- D. 4

- E. None of the above

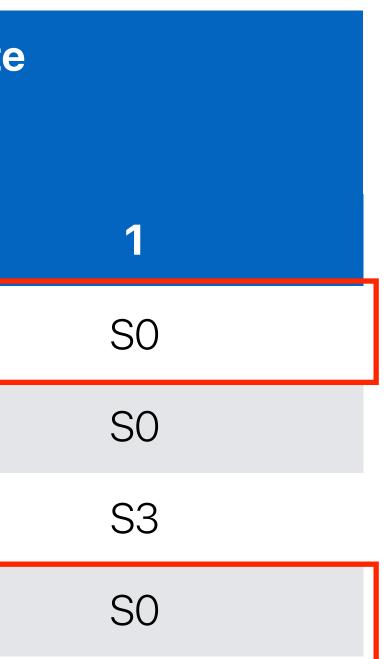

### **State Transition Table of Life on Mars**

|                     | Next | State |

|---------------------|------|-------|

| Current<br>State    | Ing  | out   |

|                     | 0    | 1     |

| S0 — something else | SO   | S1    |

| S1—1                | S2   | S1    |

| S2—10               | SO   | S3    |

| S3—101              | S2   | S1    |

- Mars rover has a binary input x. When it receives the input sequence x(t-2, t) = 101 from its life detection sensors, it means that the it has detected life on Mars and the output y(t) = 1, otherwise y(t) = 0 (no life on Mars).

- How many states in the FSM of the pattern recognizer should have

- A. 1

- B. 2

- C. 3

- D. 4

- E. None of the above

### 1/0 == Input 1/Output 0

Which of the following diagrams is a correct FSM for the "101" pattern recognizer? (If sees "101", output "1")

### (D) All are correct (E) None is correct

### 1/0 == Input 1/Output 0

Which of the following diagrams is a correct FSM for the "101" pattern recognizer? (If sees "101", output "1")

### (D) All are correct (E) None is correct

# How make FSM true?

### What do we need to physically implement the timer?

- A set of logic to display the remaining time we know how to do this already

- A logic to keep track of the "current state" memory

- A set of logic that uses the "current state" and "a new input" to transit to a new state and generate the output — we also know how to build this

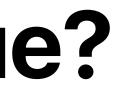

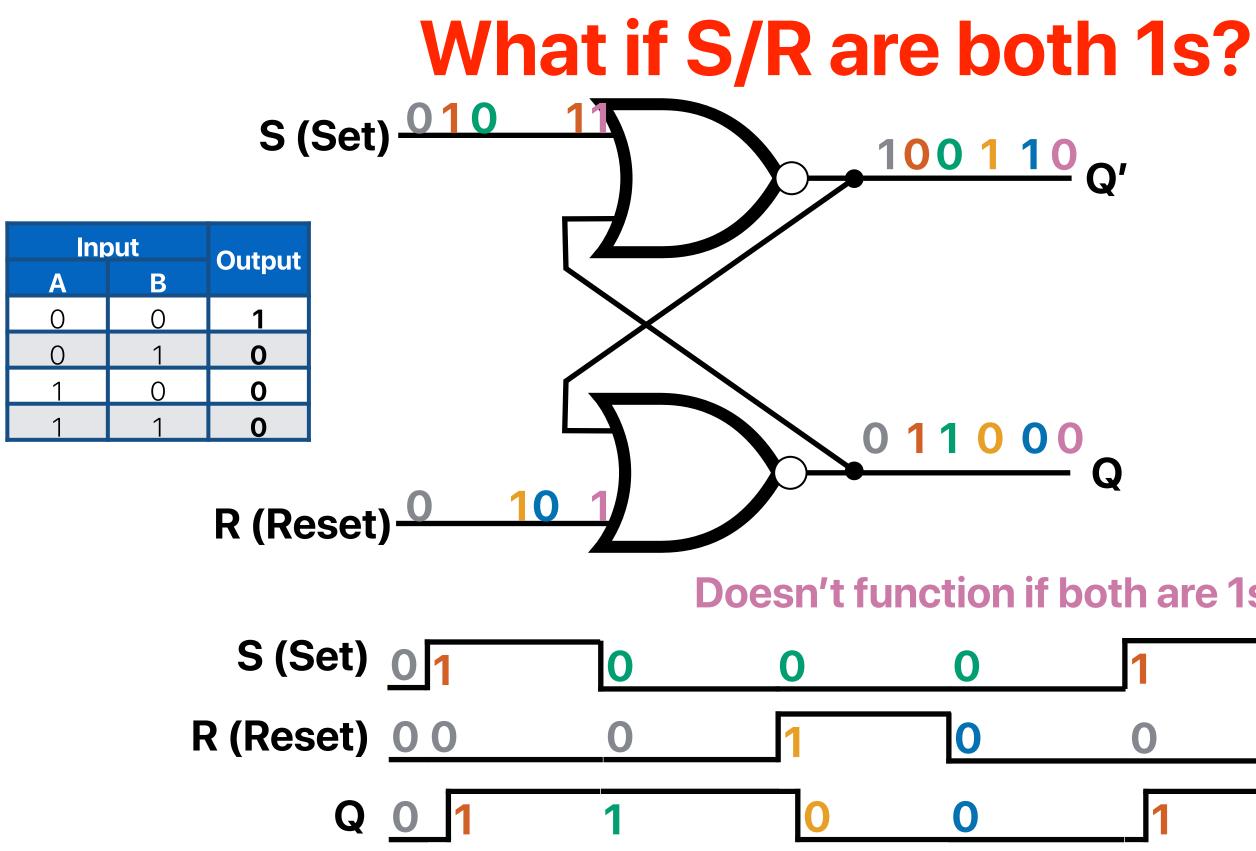

# The basic form of memory

### Set — Make the "stored bit 1" **Reset — Make the "stored bit 0"** Hold — both set/reset are 0

### The circuit has memory!

| S | R | Q(t) | Q(t+1) |

|---|---|------|--------|

| 0 | 0 | 0    | 0      |

| 0 | 0 | 1    | 1      |

| 0 | 1 | 0    | 0      |

| 0 | 1 | 1    | 0      |

| 1 | 0 | 0    | 1      |

| 1 | 0 | 1    | 1      |

| 1 | 1 | 0    |        |

| 1 | 1 | 1    |        |

|       | S | R | Q(t) | Q(t+1) |

|-------|---|---|------|--------|

|       | 0 | 0 | 0    | 0      |

|       | 0 | 0 | 1    | 1      |

|       | 0 | 1 | 0    | 0      |

|       | 0 | 1 | 1    | 0      |

|       | 1 | 0 | 0    | 1      |

|       | 1 | 0 | 1    | 1      |

|       | 1 | 1 | 0    | 0      |

|       | 1 | 1 | 1    | 0      |

| e 1s! |   |   |      |        |

| -     | 1 |   |      |        |

|       | 1 |   |      |        |

|       | 0 |   |      |        |

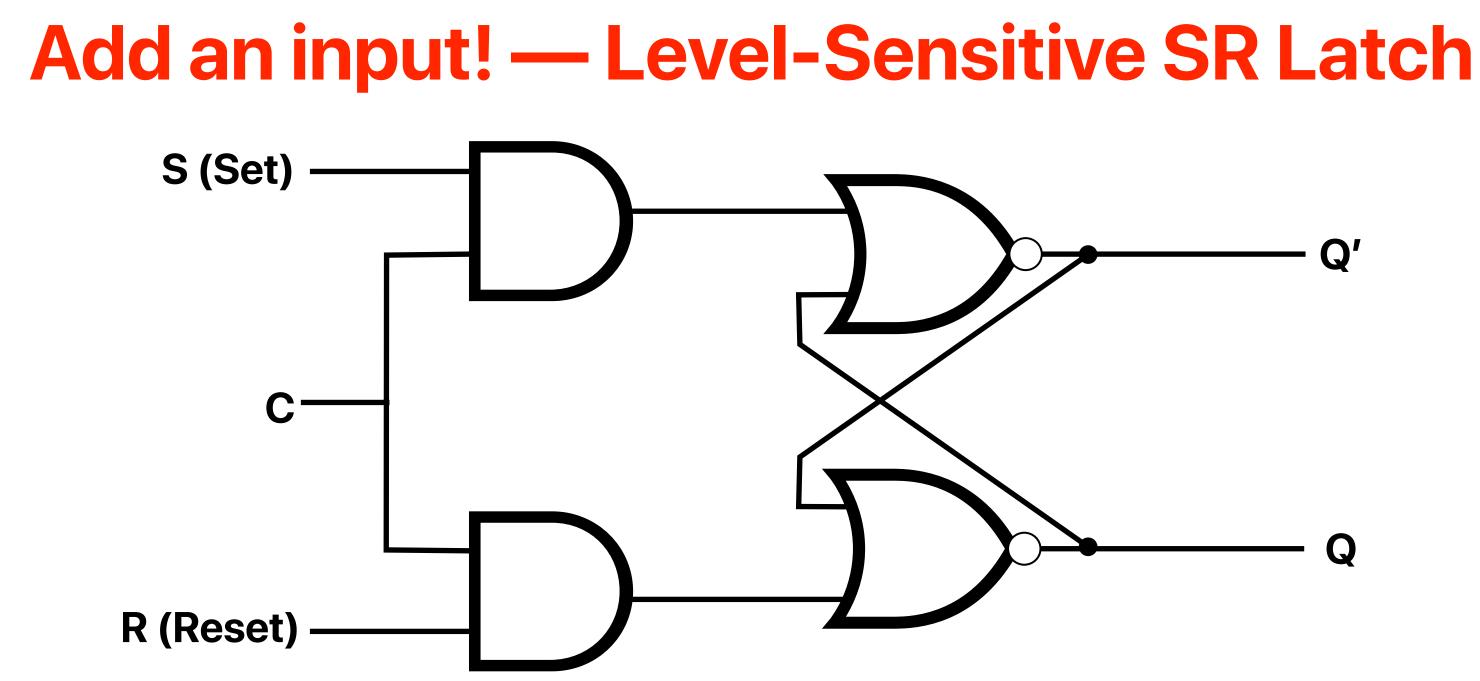

- Change C to 1 only after S and R are stable

- C is a signal aware of the **timing** of gates **clock**

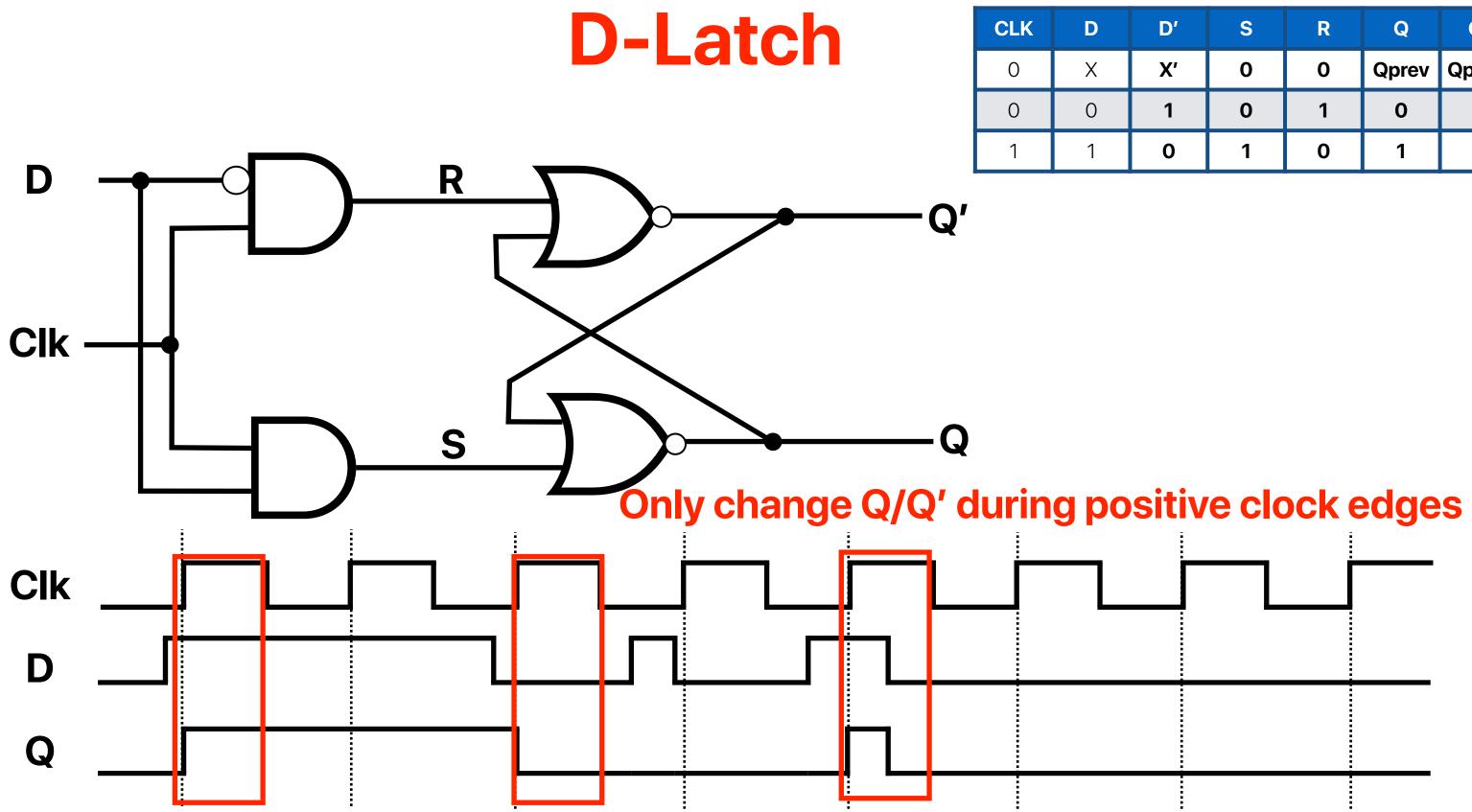

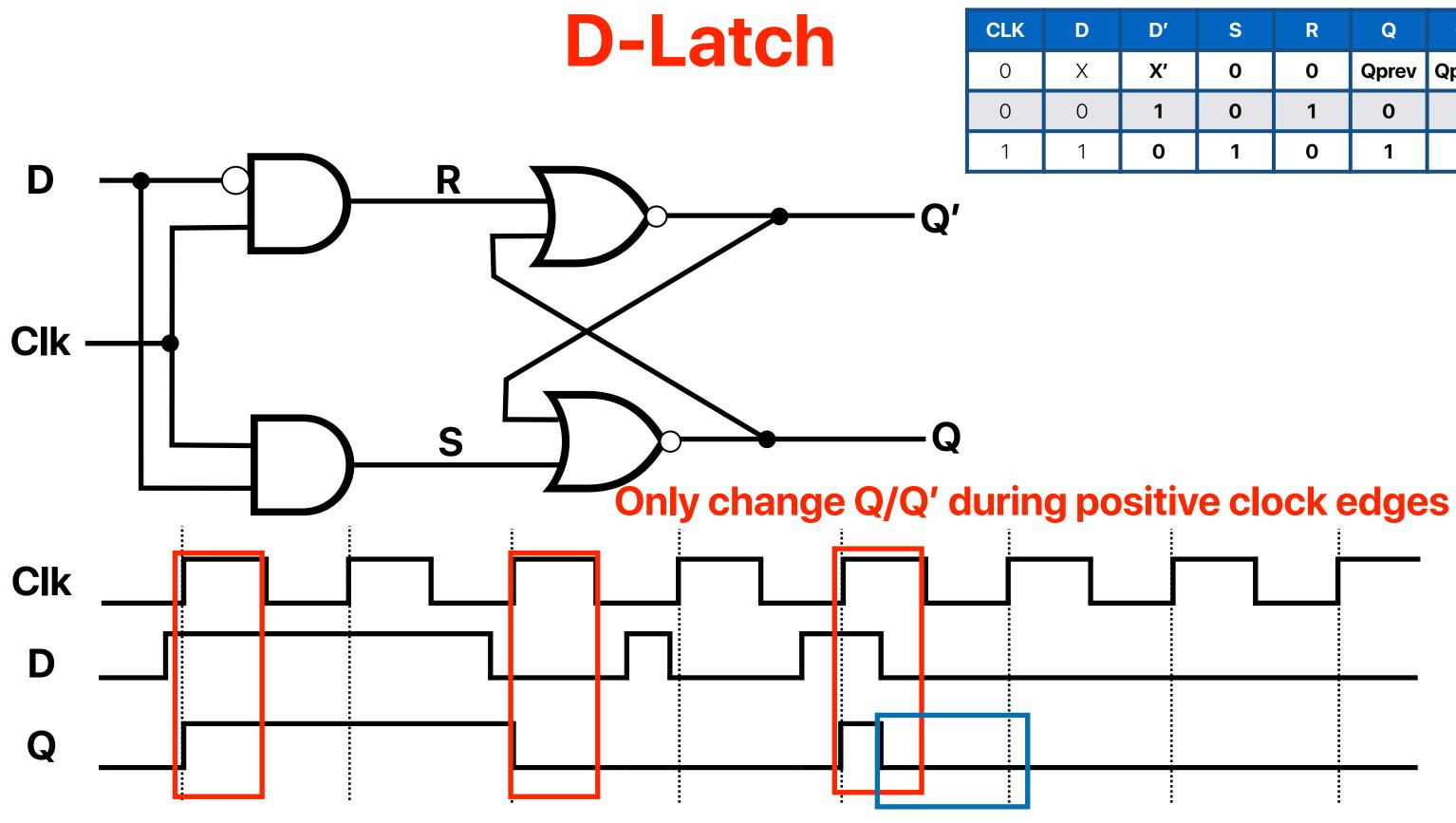

### **D-Latch**

| S | R | Q     | Q'     |

|---|---|-------|--------|

| 0 | 0 | Qprev | Qprev' |

| 0 | 1 | 0     | 1      |

| 1 | 0 | 1     | 0      |

Q'

Q

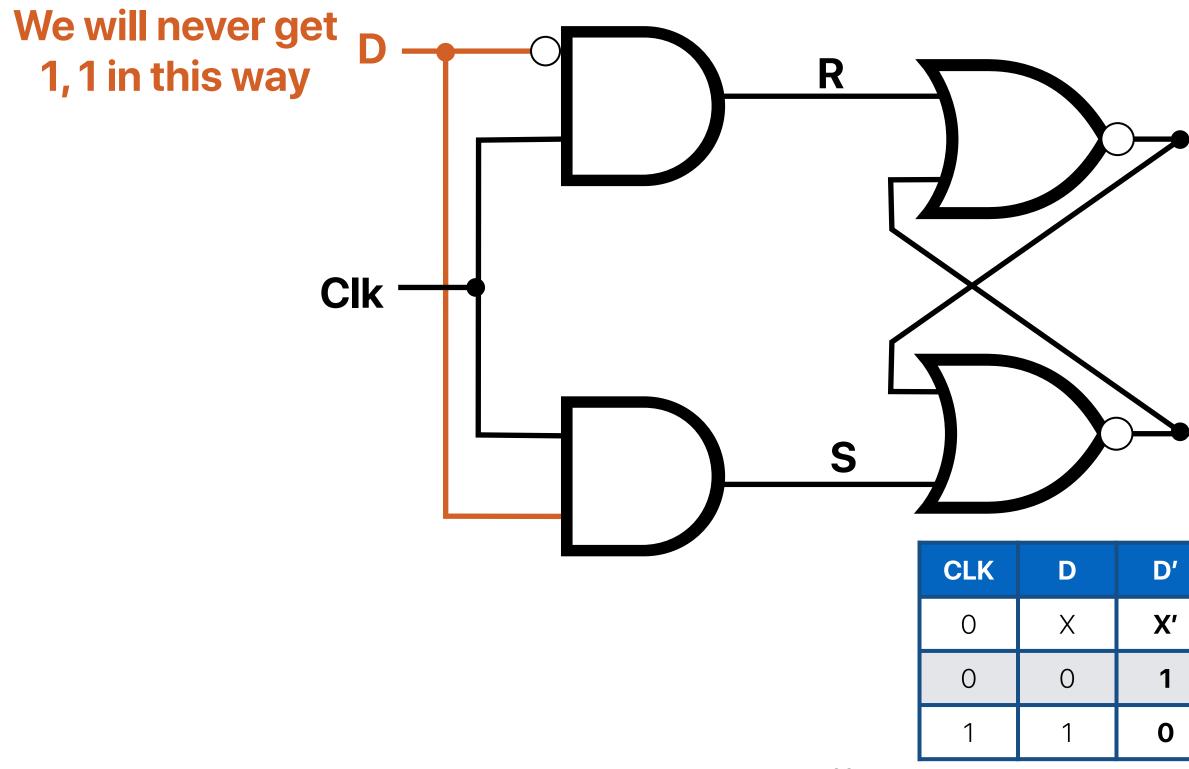

| D | D' | S | R | Q     | Q'     |

|---|----|---|---|-------|--------|

| Х | Χ′ | 0 | 0 | Qprev | Qprev' |

| 0 | 1  | 0 | 1 | 0     | 1      |

| 1 | 0  | 1 | 0 | 1     | 0      |

| D | D' | S | R | Q     | Q'     |

|---|----|---|---|-------|--------|

| Х | Χ′ | 0 | 0 | Qprev | Qprev' |

| 0 | 1  | 0 | 1 | 0     | 1      |

| 1 | 0  | 1 | 0 | 1     | 0      |

### <sup>35</sup> Output doesn't hold for the whole cycle

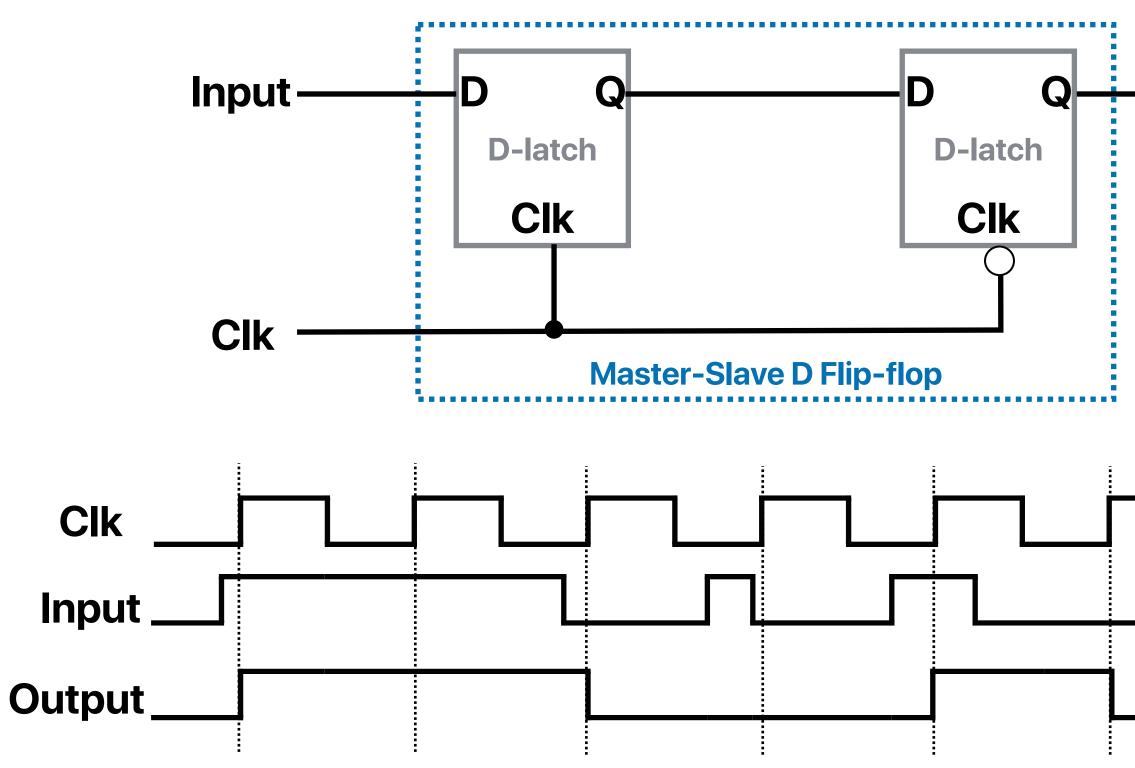

# D flip-flop

### What do we need to physically implement the timer?

- A set of logic to display the remaining time we know how to do this already

- A logic to keep track of the "current state" memory

- A set of logic that uses the "current state" and "a new input" to transit to a new state and generate the output — we also know how to build this

- A control signal that helps us to transit to the right state at the right time — clock

# The basic concept of "clock"

Poll close in 1:30

## What if?

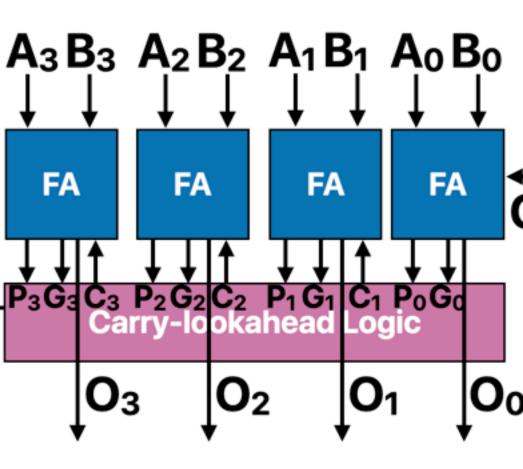

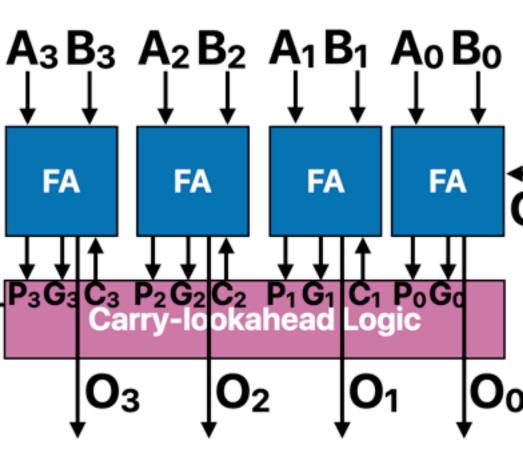

- Consider a 32-bit carrylookahead adder built with 8 4-bit carry-lookahead adders. If we take the Cout output after 4 gate delays and feed another input at that time, which of the following would be true?

- A. At the time we take the output, we can get the correct result

- B. At the time we take the output, we cannot get the correct result

- C. At the time we take the output, we cannot get the correct result, but we can get the correct result after another 8 gate delays

# What if?

- Consider a 32-bit carrylookahead adder built with 8 4-bit carry-lookahead adders. If we take the Cout output after 4 gate delays and feed another input at that time, which of the following would be true?

- A. At the time we take the output, we can get the correct result

- B. At the time we take the output, we cannot get the correct result

- C. At the time we take the output, we cannot get the correct result, but we can get the correct result after another 8 gate delays

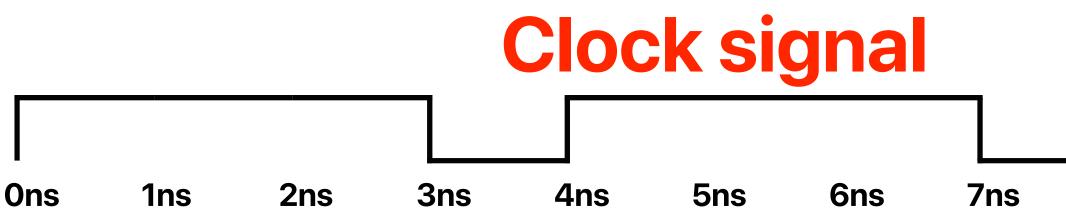

# **Clock signal**

- Clock -- Pulsing signal for enabling latches; ticks like a clock

- Synchronous circuit: sequential circuit with a clock

- Clock period: time between pulse starts

- Above signal: period = 20 ns

- Clock cycle: one such time interval

- Above signal shows 3.5 clock cycles

- Clock duty cycle: time clock is high

- 50% in this case

- Clock frequency: 1/period

- Above : freq = 1 / 20ns = 50MHz;

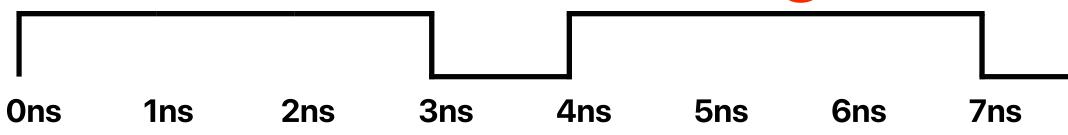

## **Clock signal**

- Regarding the above clock signal, please identify how many of the following statements are correct?

- ① Clock period of 4ns with 250MHz frequency

- ② Clock duty cycle 75%

- ③ Clock period of 1ns with 1GHz frequency

- ④ The above contains two complete clock cycles.

- A. 0

- B. 1

- C. 2

- D. 3

### E. 4

### 8ns 9ns of the following

- Regarding the above clock signal, please identify how many of the following statements are correct?

- Clock period of 4ns with 250MHz frequency

- Clock duty cycle 75%

- ③ Clock period of 1ns with 1GHz frequency

- M The above contains two complete clock cycles.

- A. 0

- B. 1

- C. 2

### 8ns 9ns of the following

## Announcement

- Lab 3 due 4/30

- Watch the video and read the instruction BEFORE your session

- There are links on both course webpage and iLearn lab section

- Submit through iLearn > Labs

- Assignment #3 due next Tuesday Chapter 3.6-3.16 & 4.1-4.4 & 4.8-4.9

- Midterm on 5/7 during the lecture time, access through iLearn

- No late submission is allowed make sure you will be able to take that at the time

- Covers: Chapter 1, Chapter 2, Chapter 3.1 3.12, Chapter 3.15 & 3.16, Chapter 4.1 4.9

- Midterm review next Tuesday (5/5) will reveal more information (e.g., review on key concepts, test format, slides of a sample midterm)

- Lab 4 is up due after final (5/12).

- Check your grades in iLearn

# Electrical Computer Science Engineering